# 第14章 差動増幅回路

信号処理を多段化する方法

差動増幅器の必要性

## 14.1 差動増幅器の機能

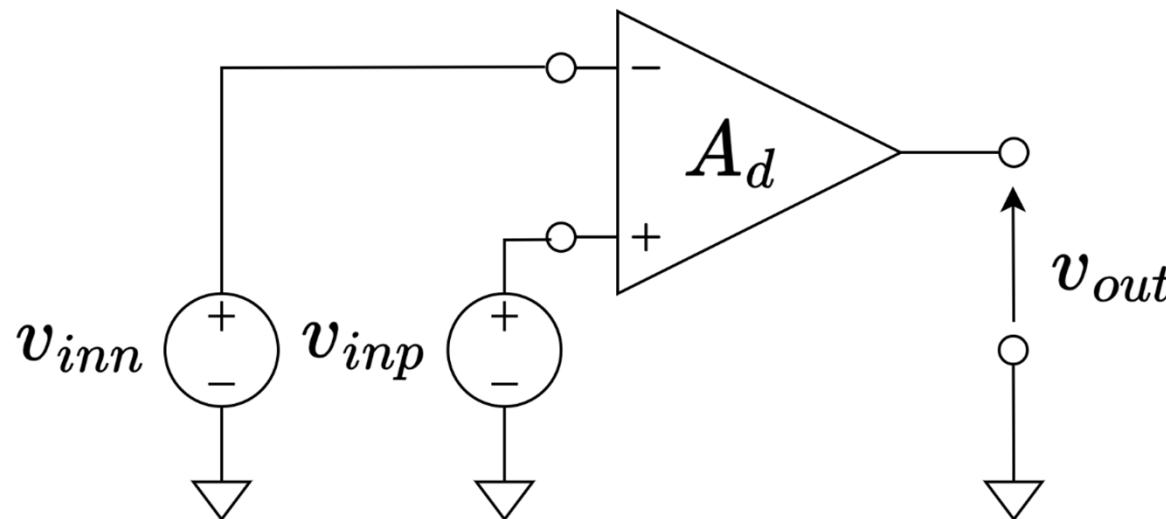

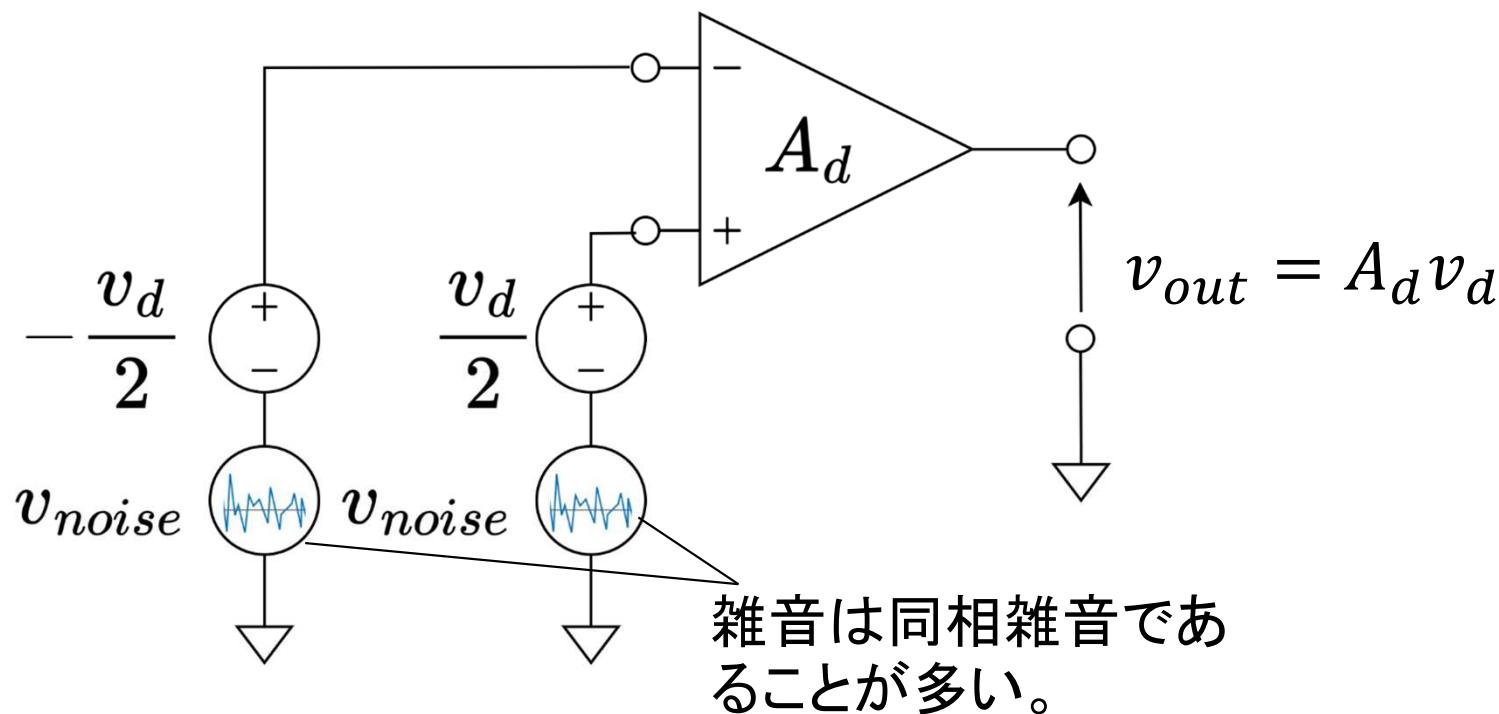

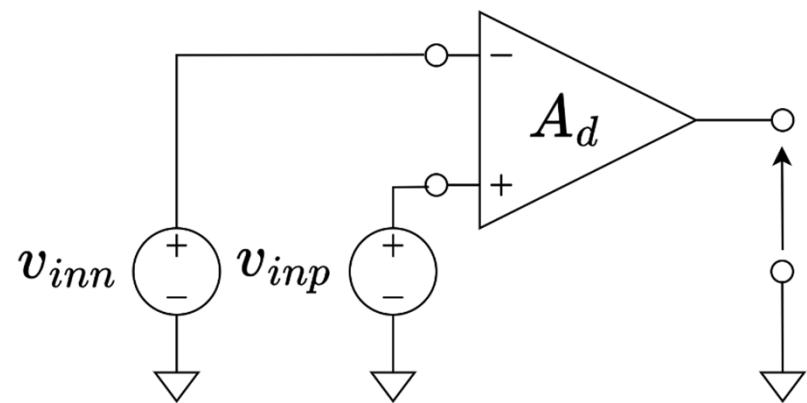

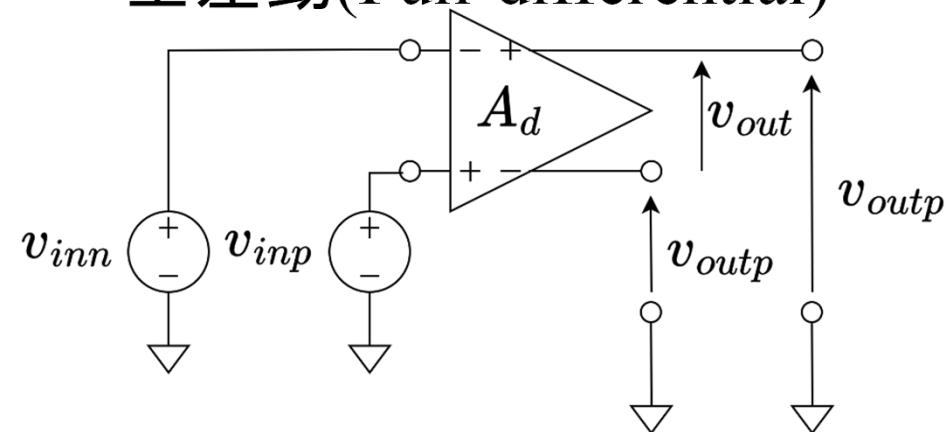

# 差動増幅器(Differential amplifier) の機能

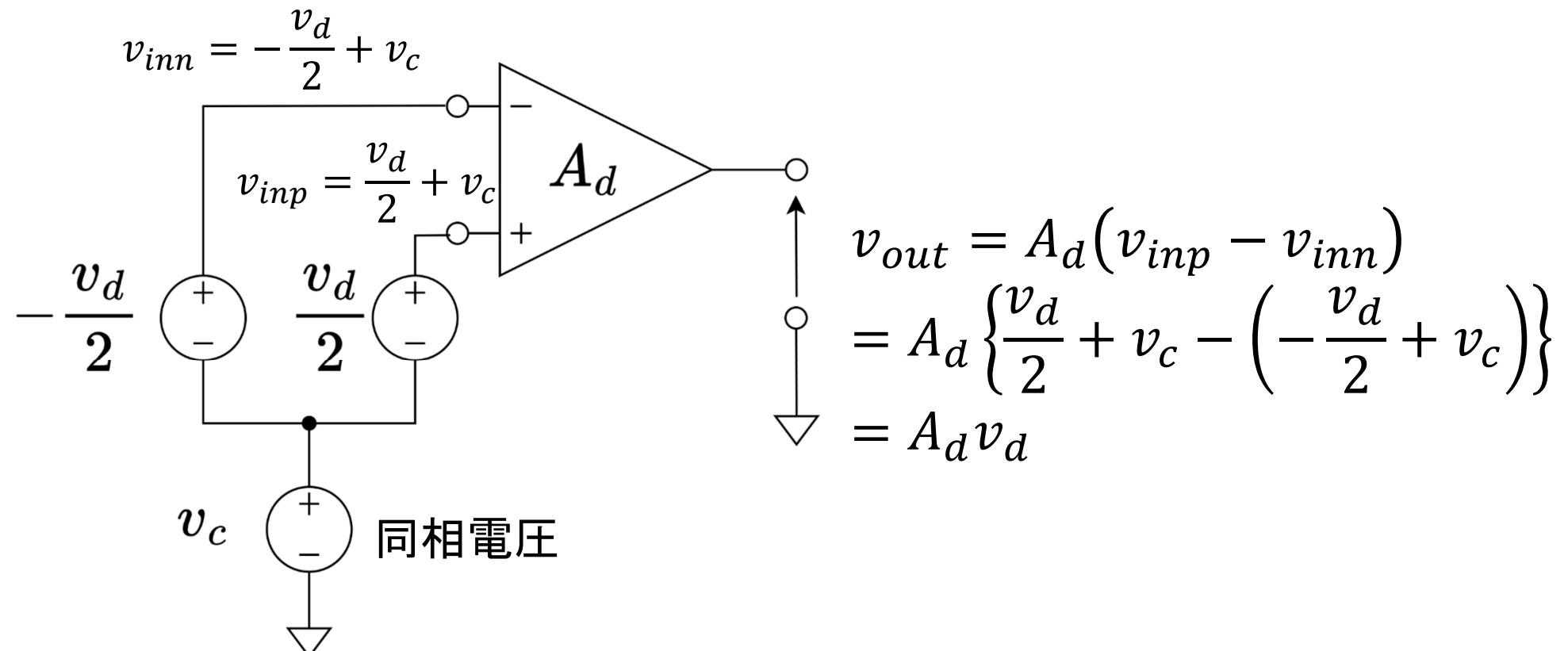

$$v_{out} = A_d(v_{inp} - v_{inn})$$

2つの入力電圧の差を取ってから増幅する。 $A_d$ は、**差動利得**(Differential gain)と呼ばれる。

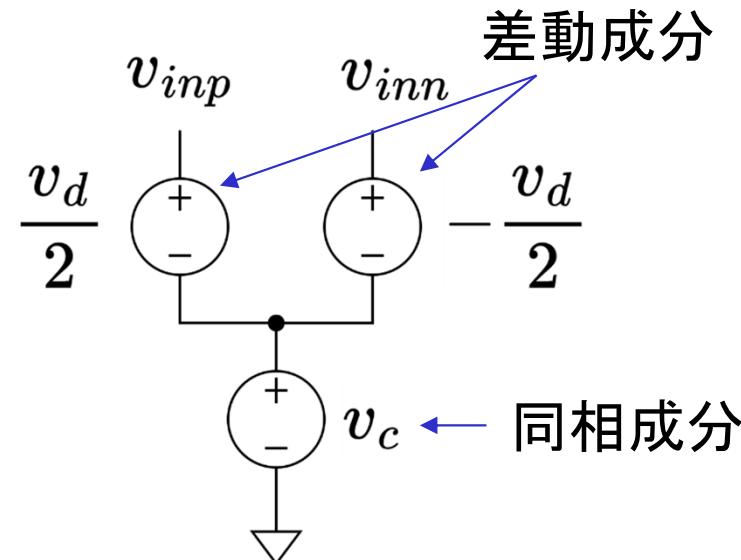

# 同相成分と差動成分

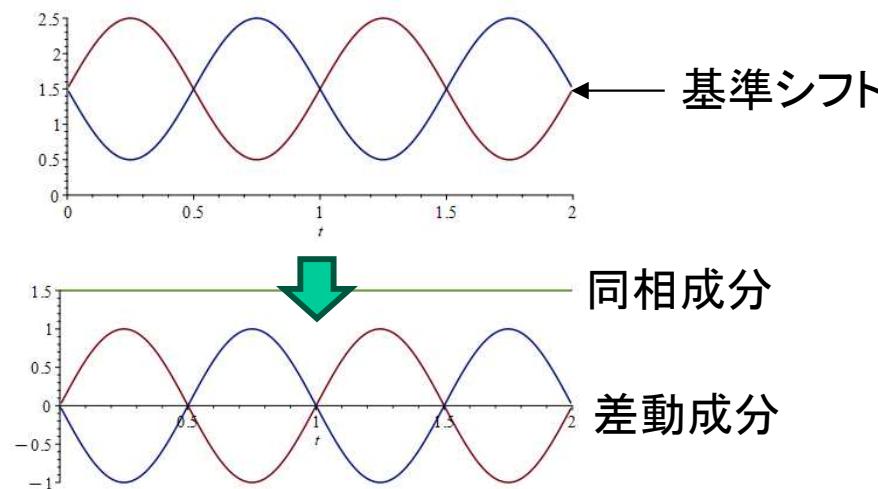

同相成分が直流の時(主にバイアス)

2つの信号波形を比較するとき、差動成分と同相成分に分解することができる。

- 逆位相の成分は**差動信号**(Differential signal)と呼ばれる

- 同位相の成分は**同相信号**(Common mode signal)と呼ばれる

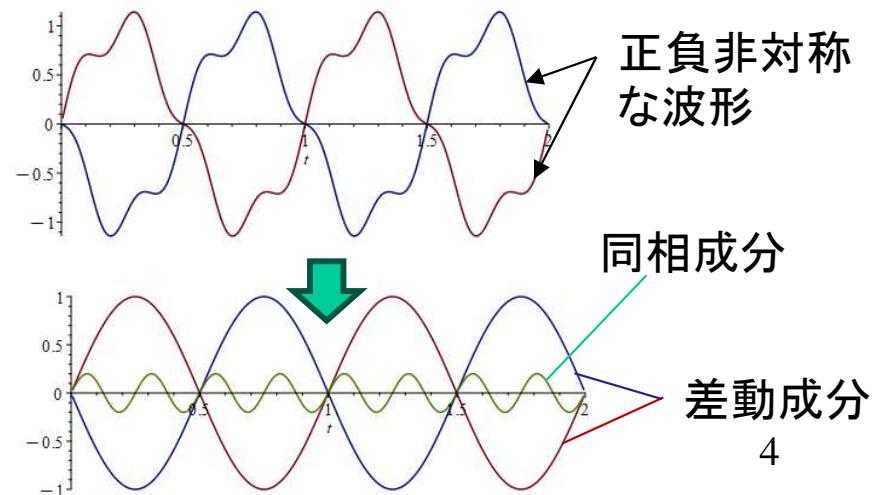

同相成分が交流の時(主に雑音、誤差)

# 差動増幅器による同相成分の除去

- 差動増幅器は、入力電圧の逆相電圧成分のみを増幅し、同相電圧成分をキャンセルする

- 直流バイアスはキャンセルされる

- 同相雑音、同相誤差はキャンセルされる

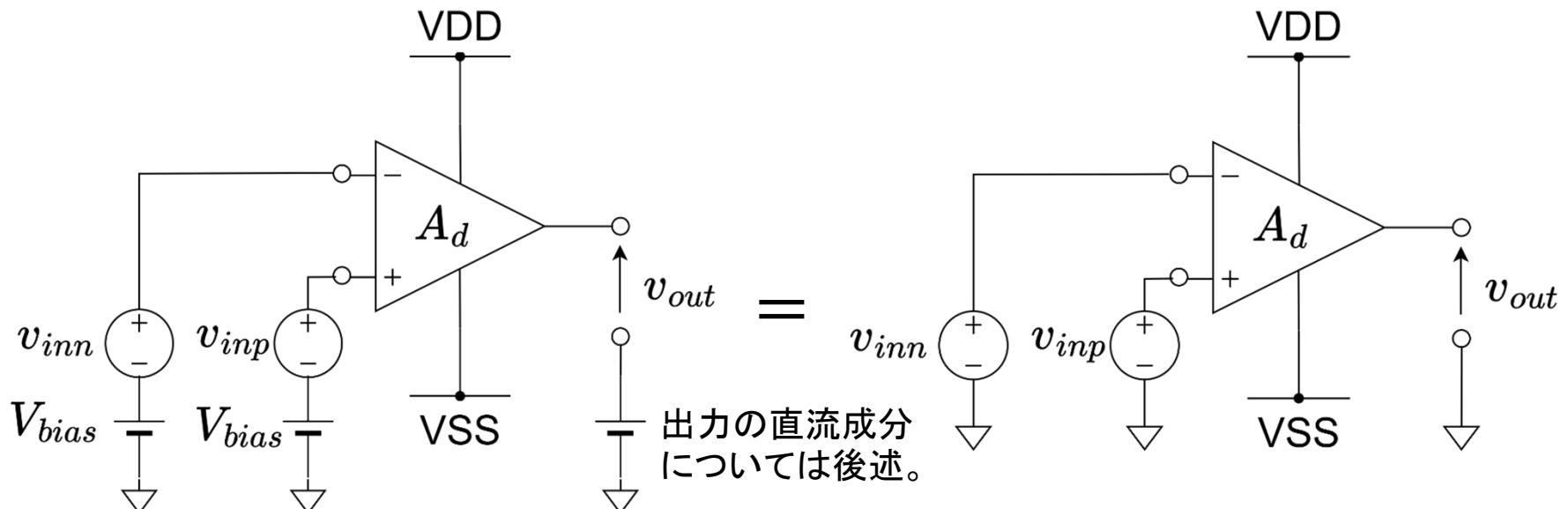

# 差動増幅器の利点1

差動増幅器の2つの入力端子に加えられたバイアス電圧は、同相電圧として除去されるため加えなくてよい。したがって、入力端子のバイアス回路は不要。

$$v_{out} = A_d \{ v_{inp} + V_{bias} - (v_{inn} + V_{bias}) \} = A_d (v_{inp} - v_{inn})$$

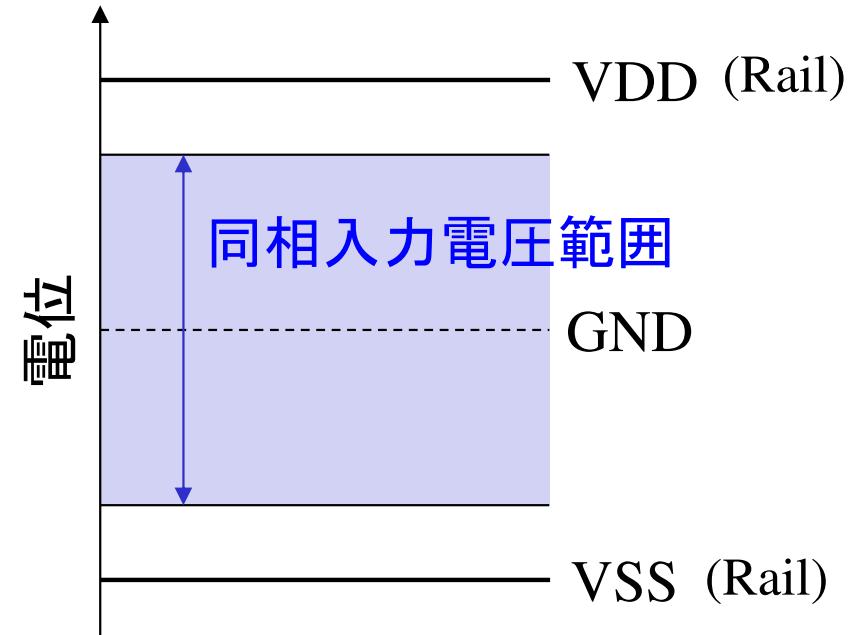

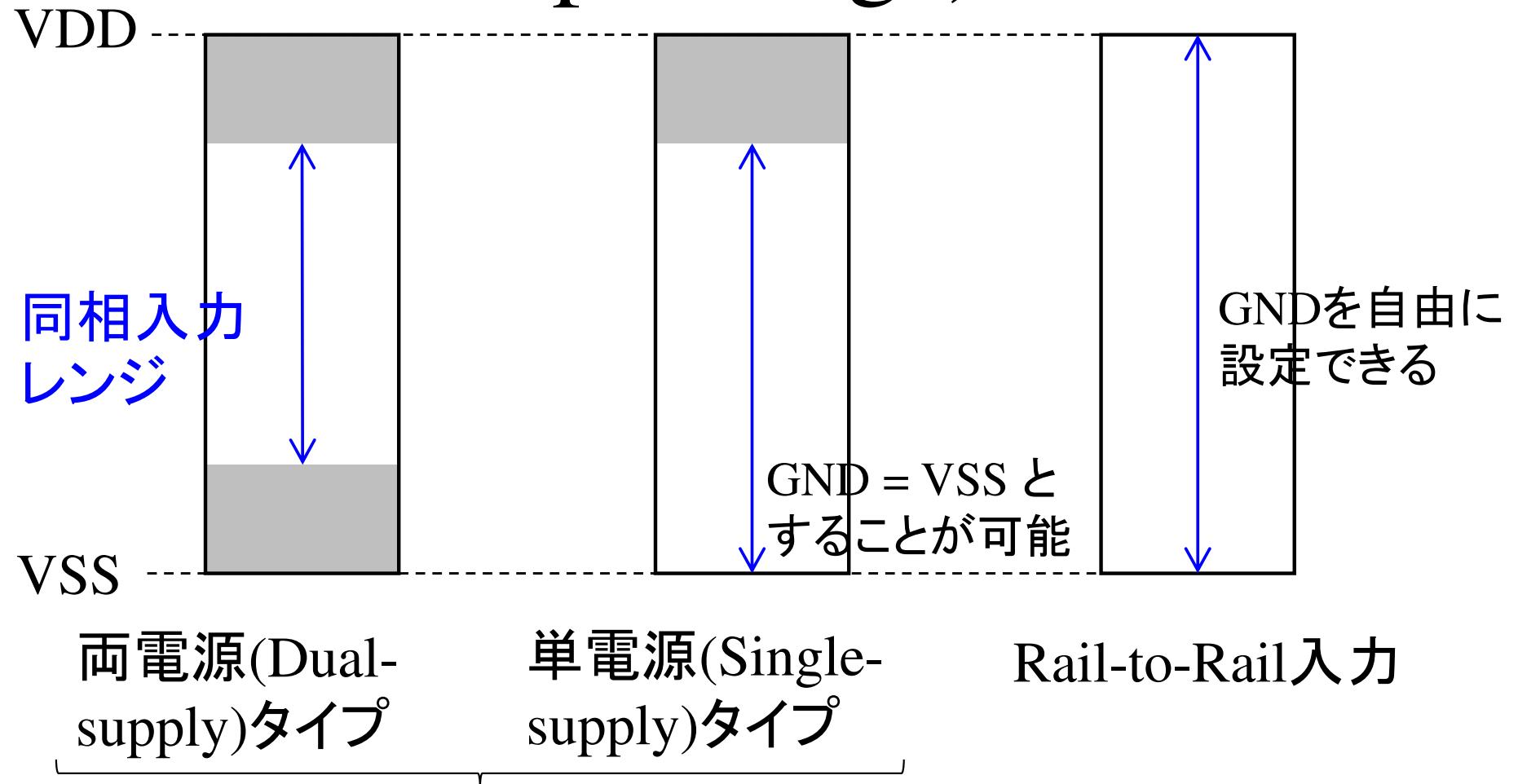

# (重要) 同相入力電圧範囲

- 差動増幅器は、バイアス電圧がない(2つの入力にバイアスを加えると除去される)ため、信号の基準となるGND電位を自由に設定できるが、**同相入力電圧範囲**(Input common-mode voltage range)内でなければならない

- 同相入力電圧範囲は、差動増幅器の回路方式に依存する

- 同相入力電圧範囲がVSS～VDDより広い差動増幅器は、**Rail-to-Rail amplifier**と呼ばれる

# 差動増幅器の利点2

同相雑音(Common-mode noise)は、差動増幅を行うと除去され、差動電圧信号のみが増幅される。同様に、偶数次の非線形歪み(MOSFETの非線形電流-電圧特性等)も除去される。

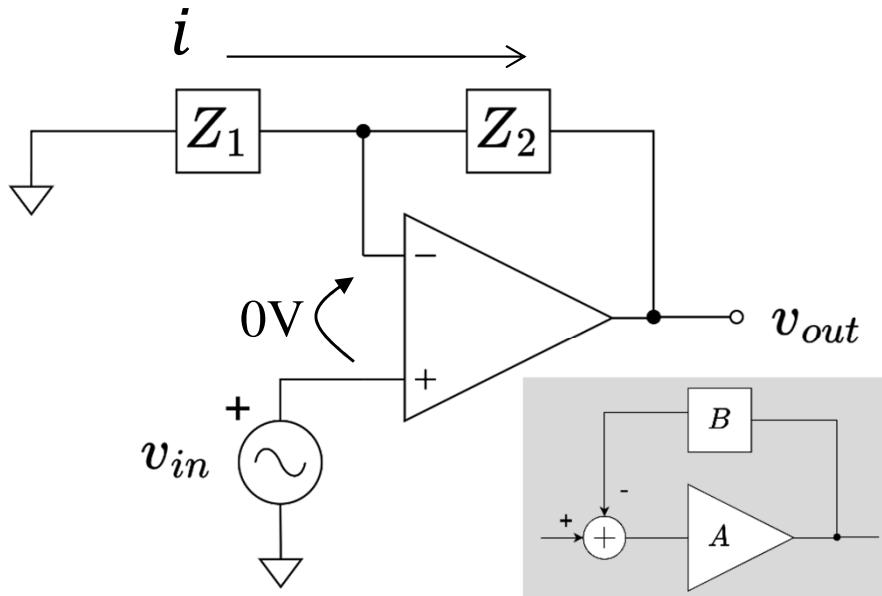

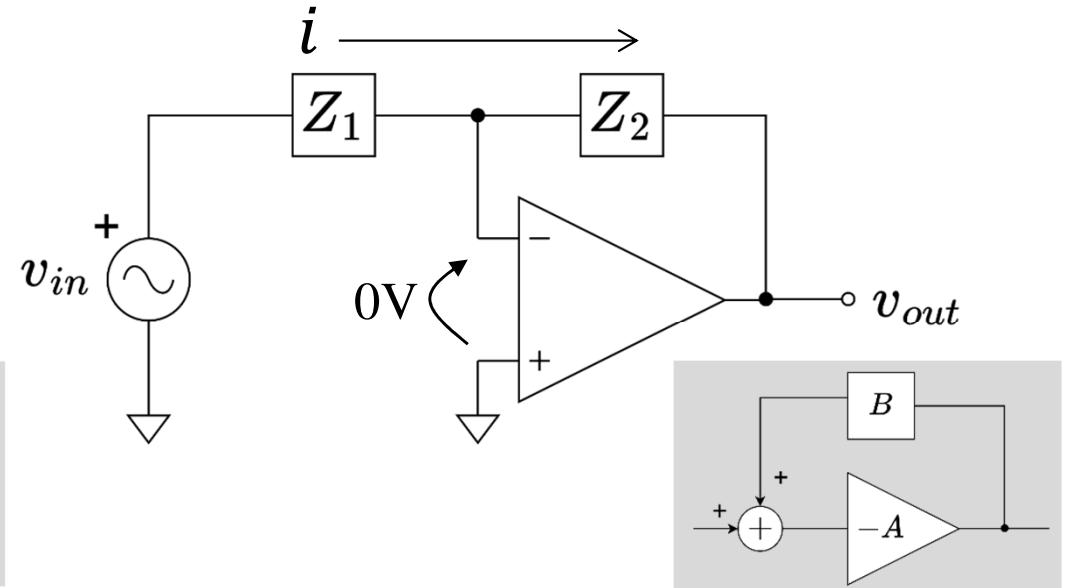

# 差動増幅器のNFB

非反転入力端子への入力

$$v_{in} = \frac{Z_1}{Z_1 + Z_1} v_{out}$$

$$\frac{v_{out}}{v_{in}} = 1 + \frac{Z_2}{Z_1}$$

反転入力端子への入力

$$\begin{cases} v_{in} = Z_1 i \\ v_{out} = Z_2 (-i) \end{cases}$$

$$\frac{v_{out}}{v_{in}} = -\frac{Z_2}{Z_1}$$

# シングルエンド型と全差動型

信号処理過程で発生した同相雑音を除去するためには、差動出力ができる全差動型増幅器を使用(離散時間回路では必須)

シングルエンド(single-end)

$$v_{out} = A_d(v_{inp} - v_{inn})$$

全差動(Full-differential)

$$v_{outp} = \frac{A_d}{2}(v_{inp} - v_{inn})$$

$$v_{outn} = -\frac{A_d}{2}(v_{inp} - v_{inn})$$

$$v_{out} = v_{outp} - v_{outn} = A_d(v_{inp} - v_{inn})$$

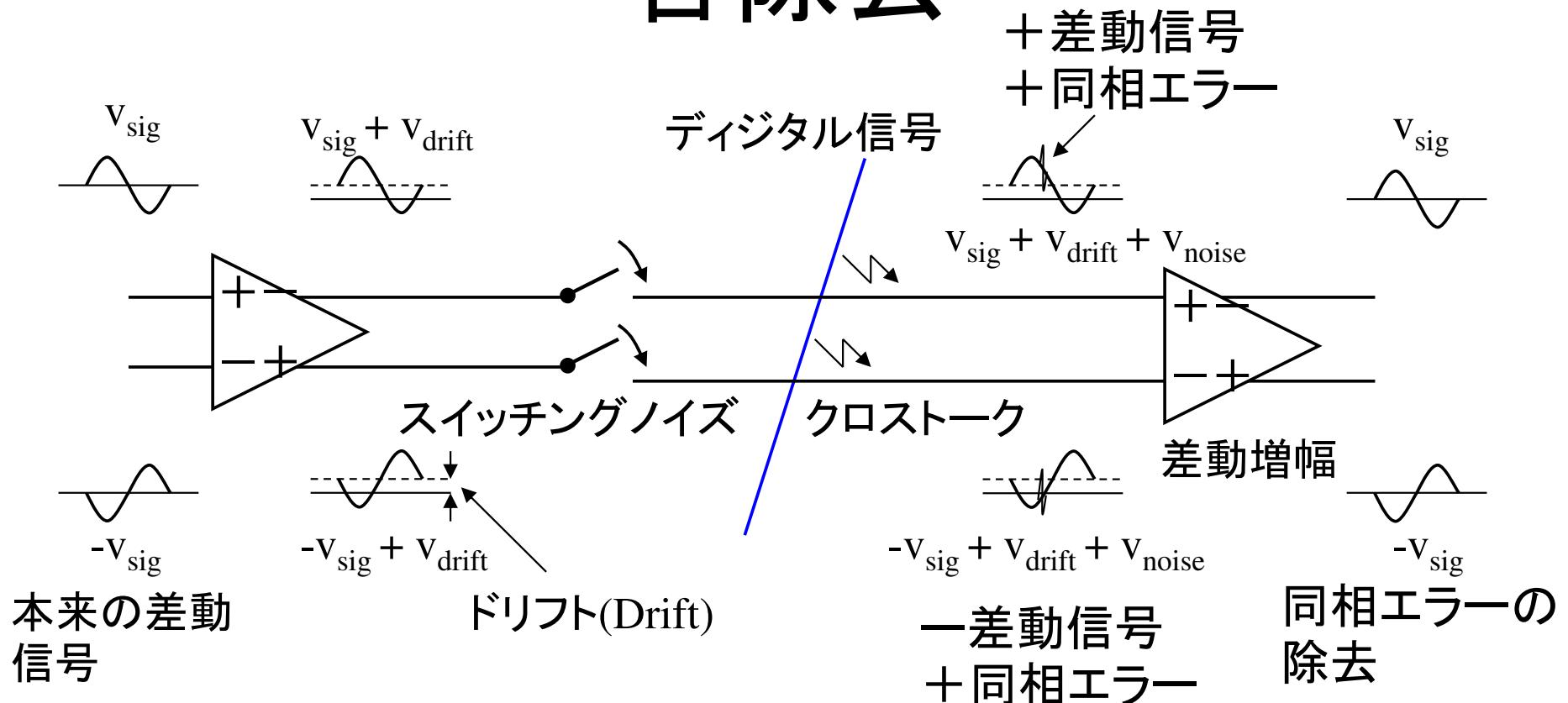

# 全差動型増幅器による同相雑音除去

Drift : 温度変化等による回路の特性変化に由来する比較的ゆっくりとした電圧や電流の同相成分変化。

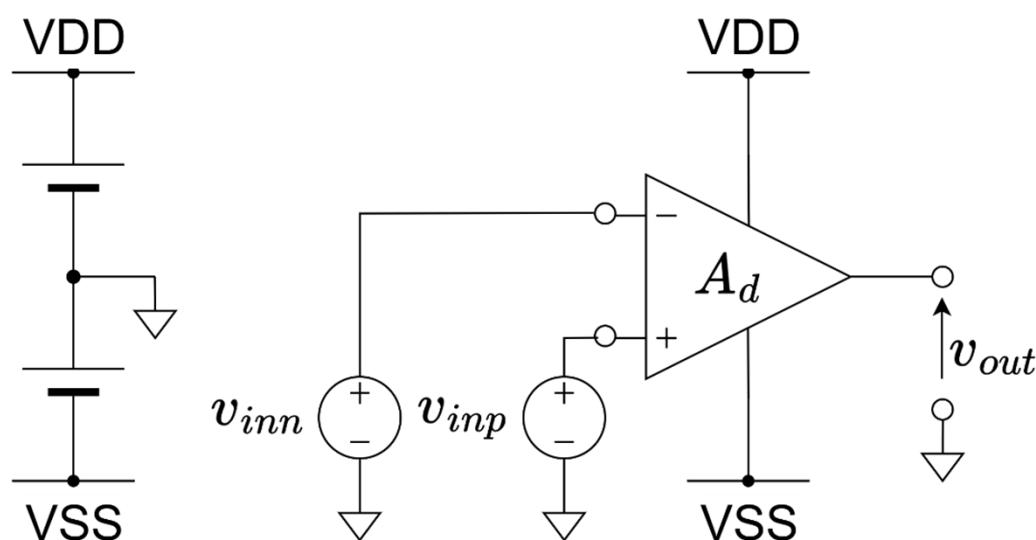

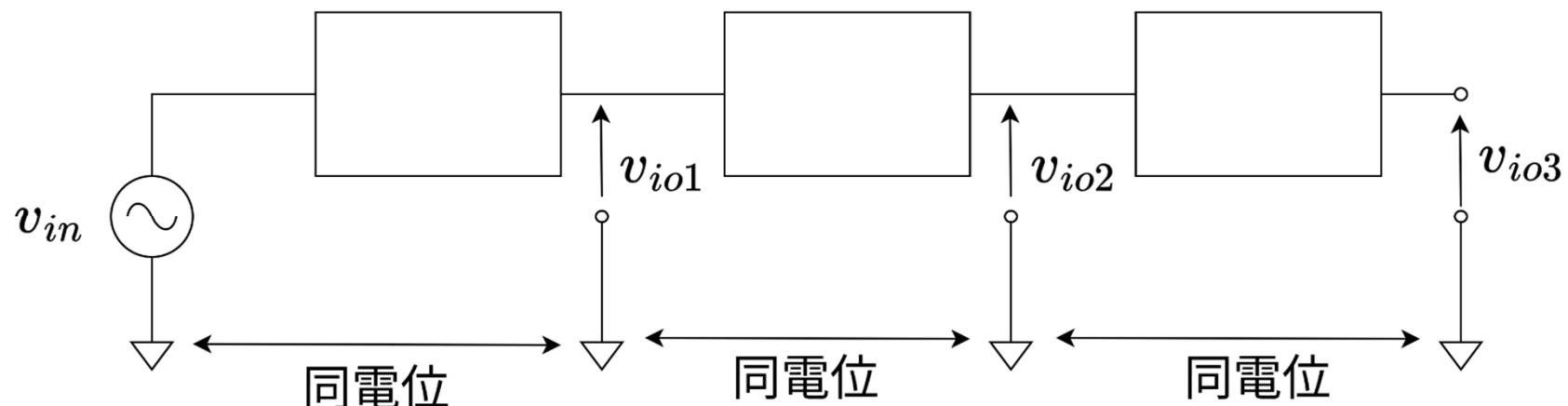

# 基本増幅回路の問題点

12章、13章で扱った基本増幅回路(ソース接地、ゲート接地、ドレイン接地増幅回路)は、入力信号の直流電圧がバイアス電圧、出力信号の直流電圧が動作点電圧となり、入力信号と出力信号で基準電位が一致するとは限らないため、直接結合による多段接続ができない。下記のように全ての入出力直流電位が同じであれば便利。

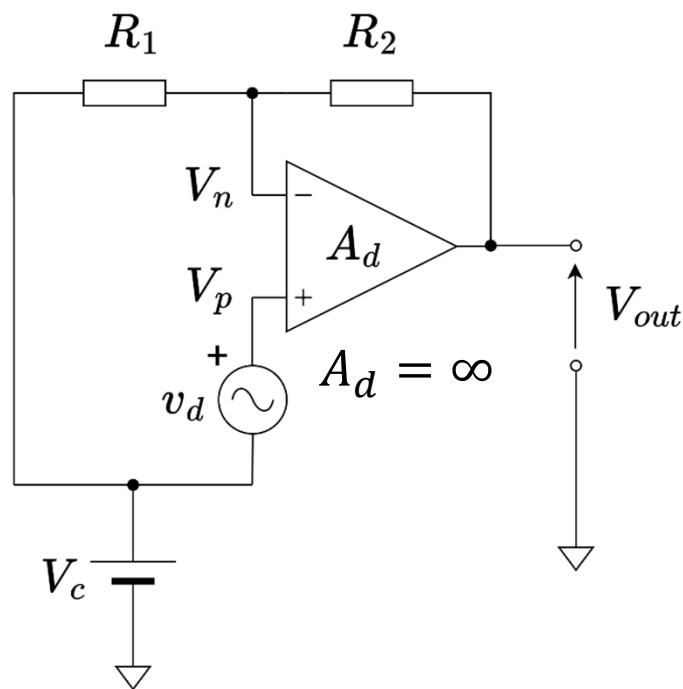

# 差動増幅回路の共通電位

差動増幅器に負帰還を行なうと、入力信号と出力信号の同相電圧が等しくなる。従って、入出力信号と出力信号の直流電圧が自動的に一致し、共通電位が設定される。

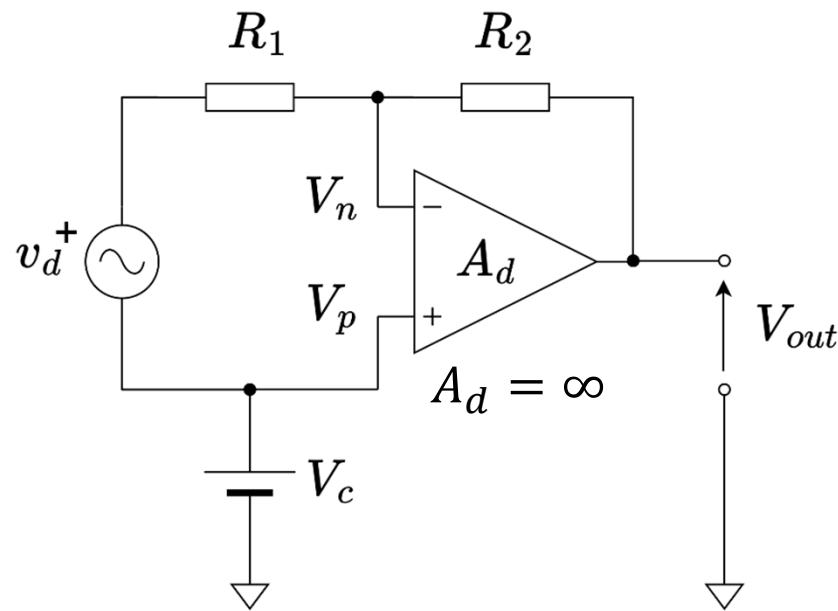

$$\begin{cases} V_p = V_c \\ V_n = \frac{R_1}{R_1 + R_2} (V_{out} - v_d - V_c) + v_d + V_c \\ V_p - V_n = 0 \quad (\text{仮想ショート}) \end{cases}$$

$$V_{out} = -\frac{R_2}{R_1} v_d + V_c$$

入出力の直流電圧が一致

# クイズ

下記の回路について、 $A_d = \infty$ としたときの出力の直流電圧を求めよ

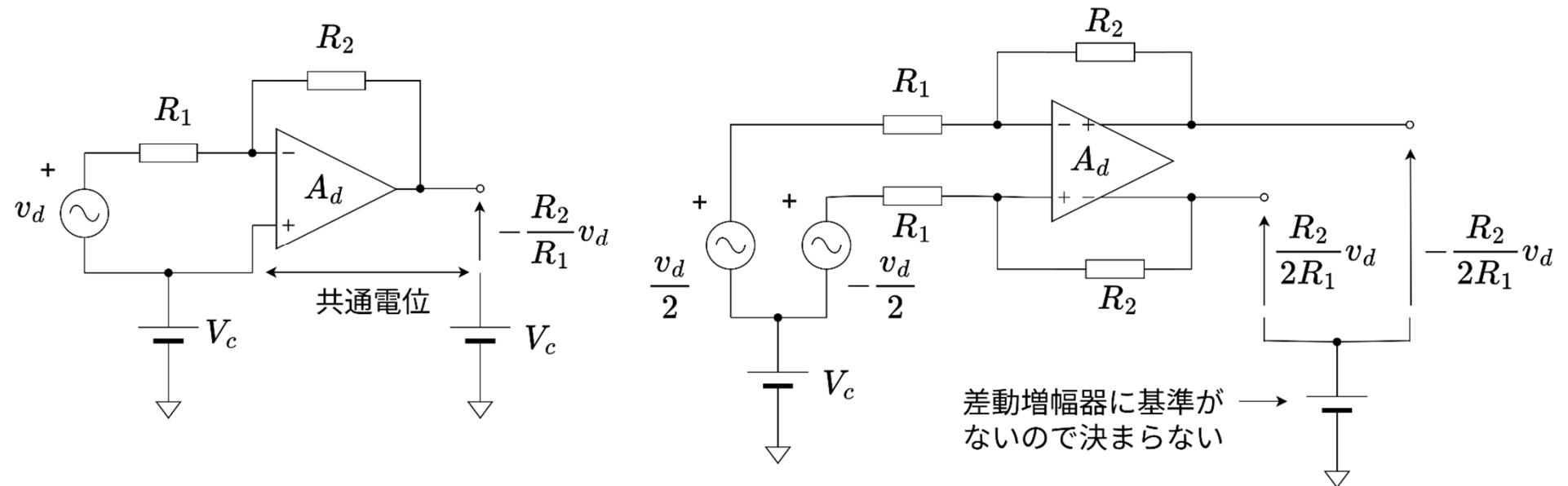

# 全差動型増幅器の共通電位

シングルエンド型は、+入力の直流電位を基準にして、入出力の共通電位を決められるが、全差動増幅器の出力電圧の直流成分は不定。

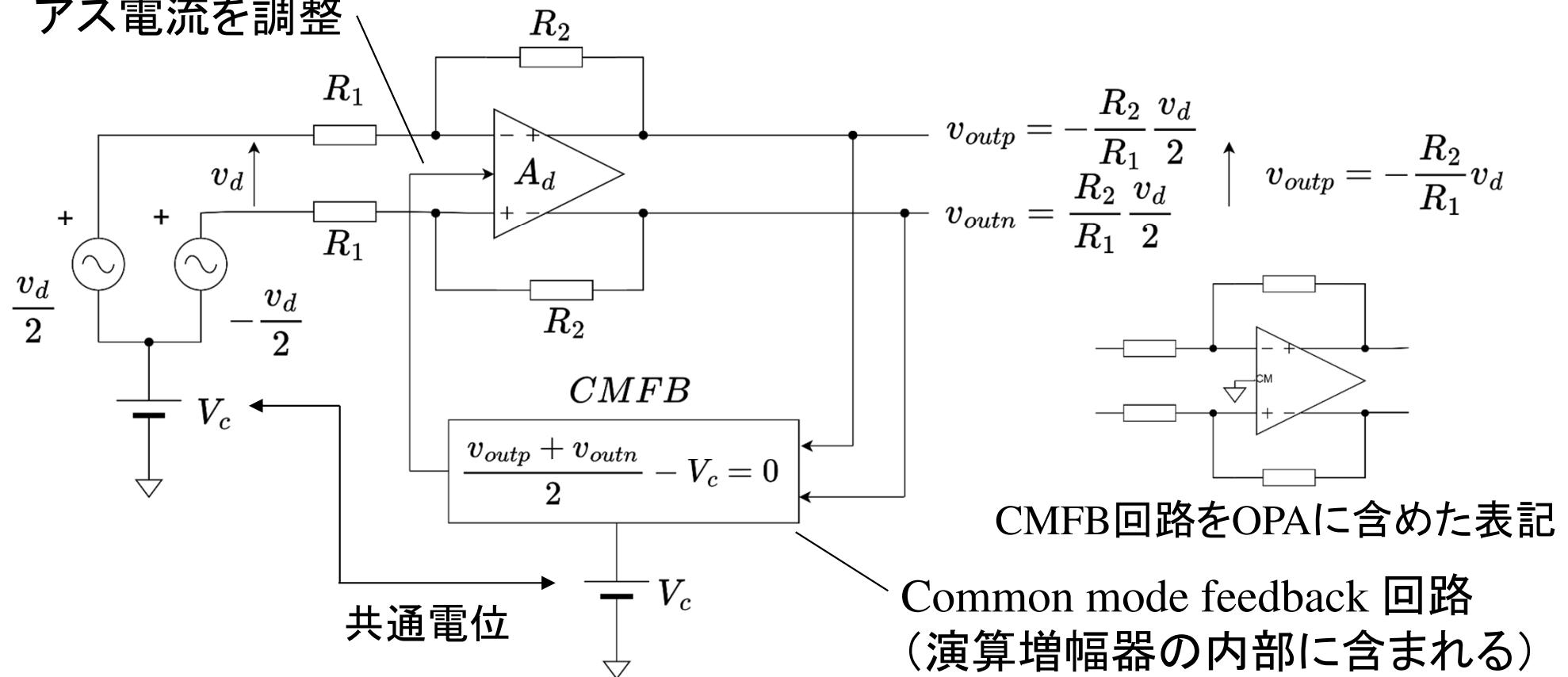

# コモンモードフィードバック

差動出力の平均値を $V_c$ に合わせるように負帰還を行なう。

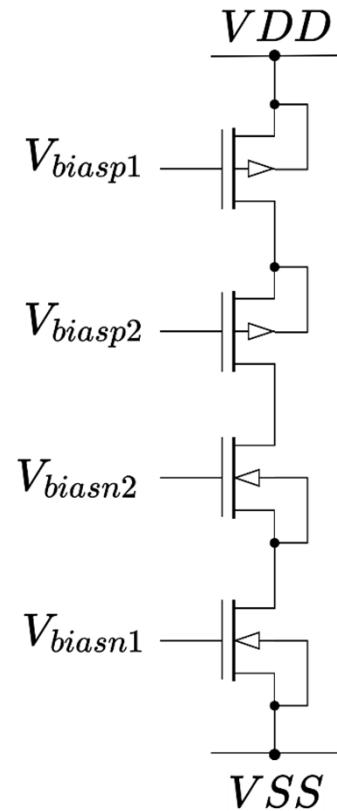

差動増幅器のバイ

アス電流を調整

MOSFETを用いた差動増幅回路の設計

## 13.2 差動増幅回路の構造と特性

# 差動増幅回路の動作原理

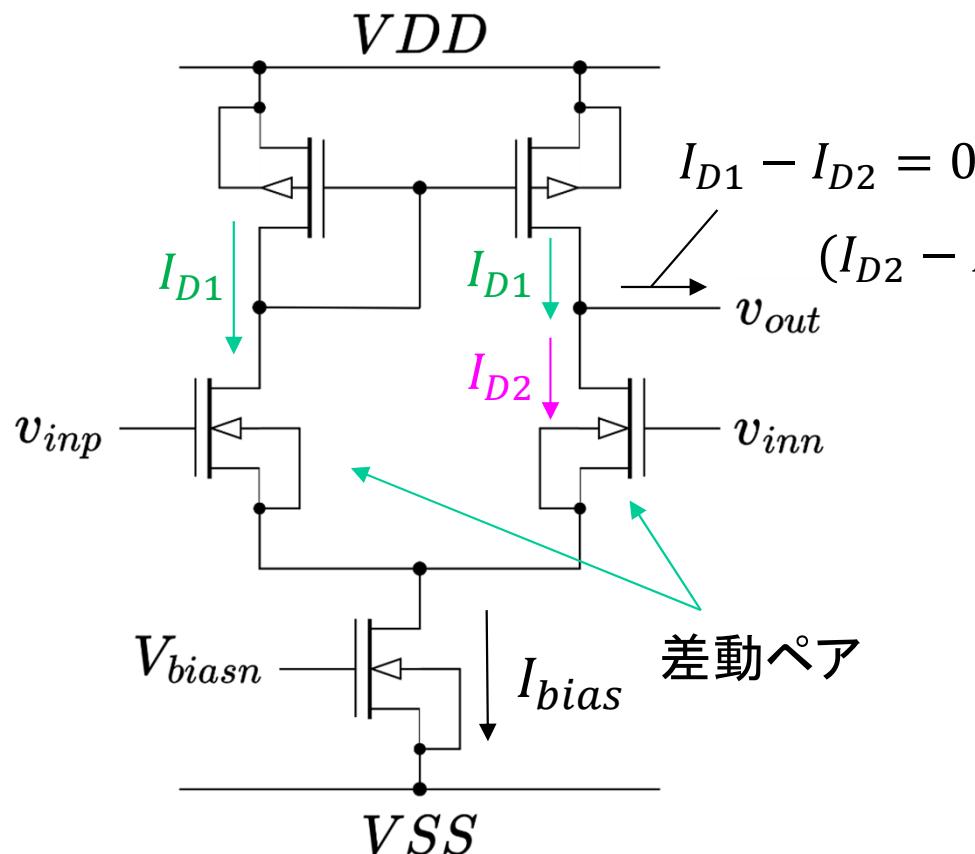

シングルエンド型

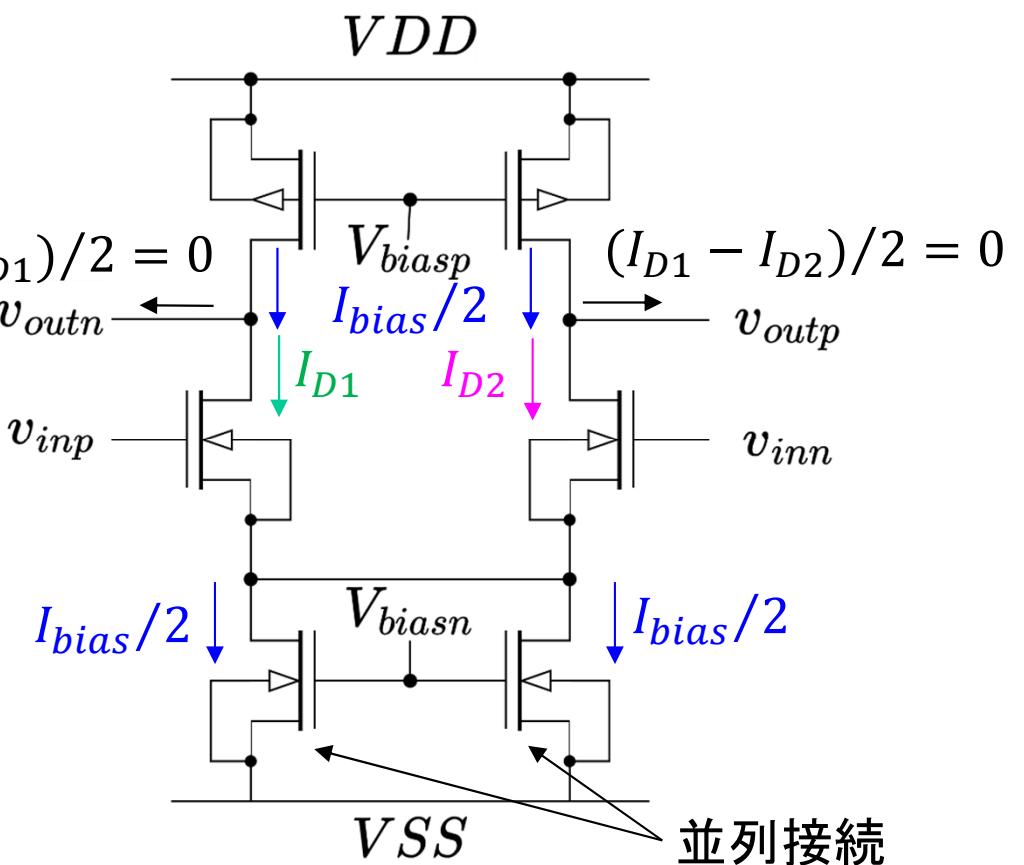

全差動型

$$I_{bias} = I_{D1} + I_{D2}$$

$$I_{bias} = I_{D1} + I_{D2}$$

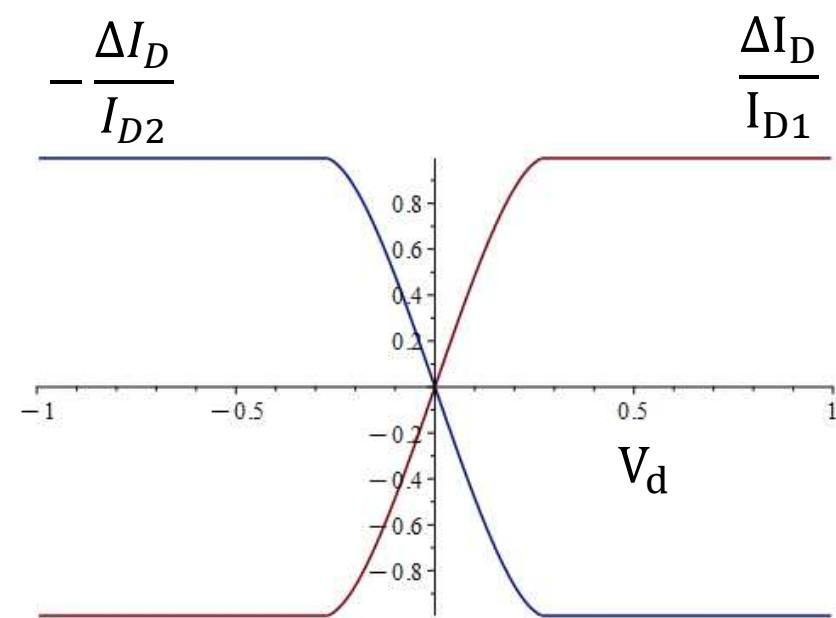

# 差動増幅回路の直流特性

前ページスライドより、出力電流 = 0 のとき  $I_{D1} = I_{D2}$

差動電圧成分を  $V_d$ 、差動入力による電流の変化分を  $\pm \Delta I_D$  とすると、

$$\begin{aligned} V_d &= v_{inp} - v_{inn} = V_{OV1} - V_{OV2} \\ &= \sqrt{\frac{2}{\beta}} (\sqrt{I_{D1} + \Delta I_D} - \sqrt{I_{D2} - \Delta I_D}) \\ &= \sqrt{\frac{2}{\beta}} (\sqrt{I_{D1} + \Delta I_D} - \sqrt{I_{D1} - \Delta I_D}) \end{aligned}$$

$$\frac{\Delta I_D}{I_{D1}} = \frac{V_d}{V_{OV1}} \sqrt{1 - \frac{1}{4} \left( \frac{V_d}{V_{OV1}} \right)^2}$$

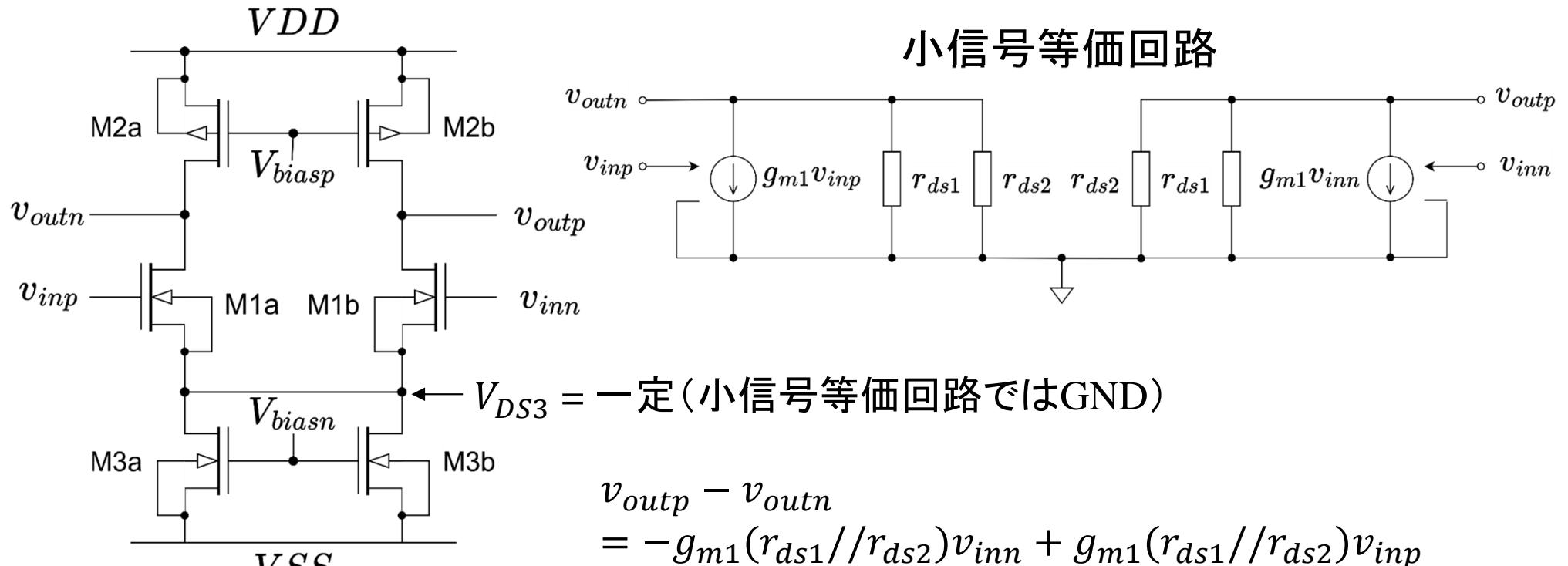

# 差動利得(Differential gain)

差動入力の場合、M3a, M3bの電流は一定なので、 $V_{DS3}$ は変化しない(GNDと等価)。

$$\begin{aligned} v_{outp} - v_{outn} &= -g_{m1}(r_{ds1}/r_{ds2})v_{inn} + g_{m1}(r_{ds1}/r_{ds2})v_{inp} \\ &= g_{m1}(r_{ds1}/r_{ds2})(v_{inp} - v_{inn}) \end{aligned}$$

$$A_d = \frac{v_{outp} - v_{outn}}{v_{inp} - v_{inn}} = g_{m1}(r_{ds1}/r_{ds2})$$

ソース接地増幅回路と同じ大きさ

# クイズ

シングルエンド型差動増幅器についても、小信号等価回路を作成して、差動利得を求めてみよう。

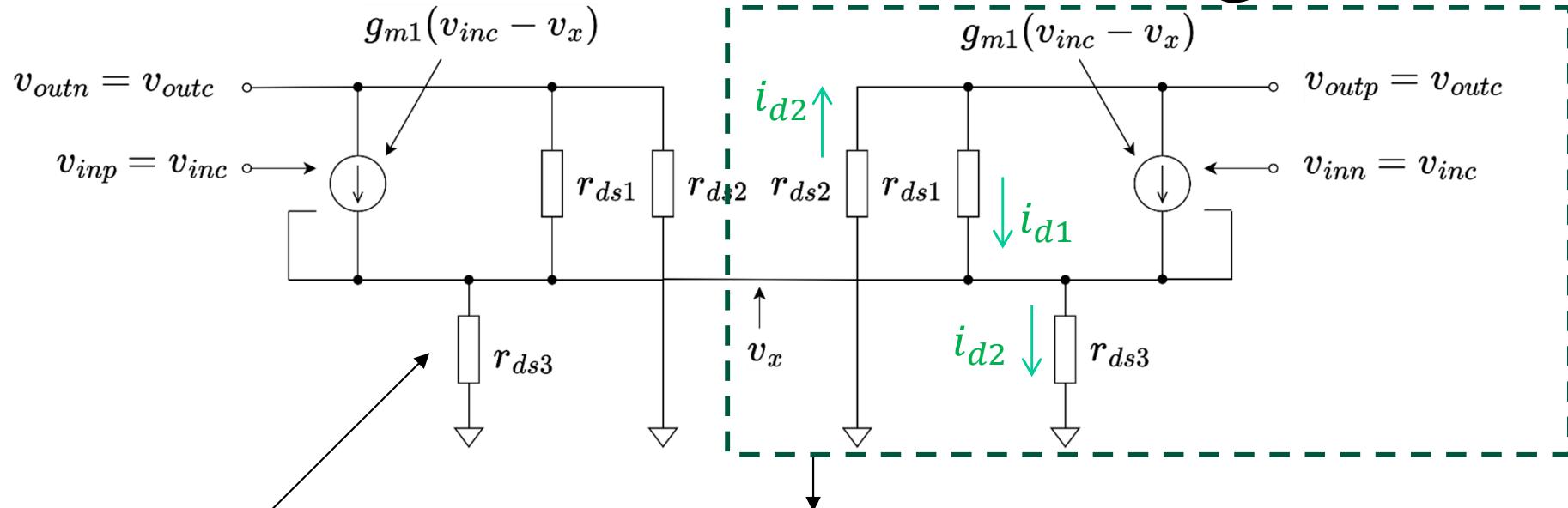

# 同相利得(Common mode gain)

同相入力のとき、 $V_{DS3} \neq$

一定(小信号等価回路で

$r_{ds3}$ を考慮する)

$r_{ds3}$  (M3a, b)がないと、 $A_c$ の

大きさは差動利得と同じに

なってしまう。

$$\begin{cases} v_{outc} = -r_{ds2}i_{d2} = r_{ds1}i_{d1} + r_{ds3}i_{d2} \\ v_x = r_{ds3}i_{d2} \\ i_{d2} = g_{m1}(v_{inc} - v_x) + i_{d1} \end{cases}$$

$$A_c = \frac{v_{outc}}{v_{inc}} = -\frac{g_{m1}(r_{ds1}/r_{ds2})}{1 + r_{ds3} \frac{1 + g_{m1}r_{ds1}}{r_{ds1} + r_{ds2}}}$$

# クイズ

シングルエンド型差動増幅器についても、同相利得を求めてみよう。

|

# CMRR(Common mode rejection ratio)

$A_c \neq 0$ では、同相成分が完全に除去できない。

差動成分のみを増幅し、同相成分を除去する差動増幅器が理想的。差動増幅器の性能指標として

**CMRR(Common mode rejection ratio)**が用いられる。

$$CMRR = \left| \frac{A_d}{A_c} \right| = \frac{g_{m1}(r_{ds1}/r_{ds2})}{\frac{g_{m1}(r_{ds1}/r_{ds2})}{1 + r_{ds3} \frac{1 + g_{m1}r_{ds1}}{r_{ds1} + r_{ds2}}}} = 1 + r_{ds3} \frac{1 + g_{m1}r_{ds1}}{r_{ds1} + r_{ds2}}$$

$$r_{ds3} = \infty \text{ のとき } CMRR = \infty$$

(M3a, M3bは無くても差動増幅は可能だが、M3a, M3bにより、

同相除去を行っている。 $I_{D3}$ が小さい方が、 $r_{ds3}$ が大きくなり

CMRRに対して有利)

# (参考) CMRRが低い差動増幅回路の問題点

- ・ 小信号等価回路の解析結果から、全差動増幅回路では、 $A_C \neq 0$ であっても、差動出力に同相成分は現れない。また、シングルエンド型は、M3が無くても  $A_C \approx g_{m1}/g_{m2}$  となるので、M3またはM3a, M3bは必要がないのではないかと考えた人もいるかもしれない。

- ・ M3またはM3a, M3bがない場合、M1a, M1bまたはM2a, M2bの特性が、僅かにズレたとき、無視できない同相信号が出力に現れる可能性があるため、CMRRをできるだけ大きくするために、M1, M2の特性とは独立したM3が必要となる。

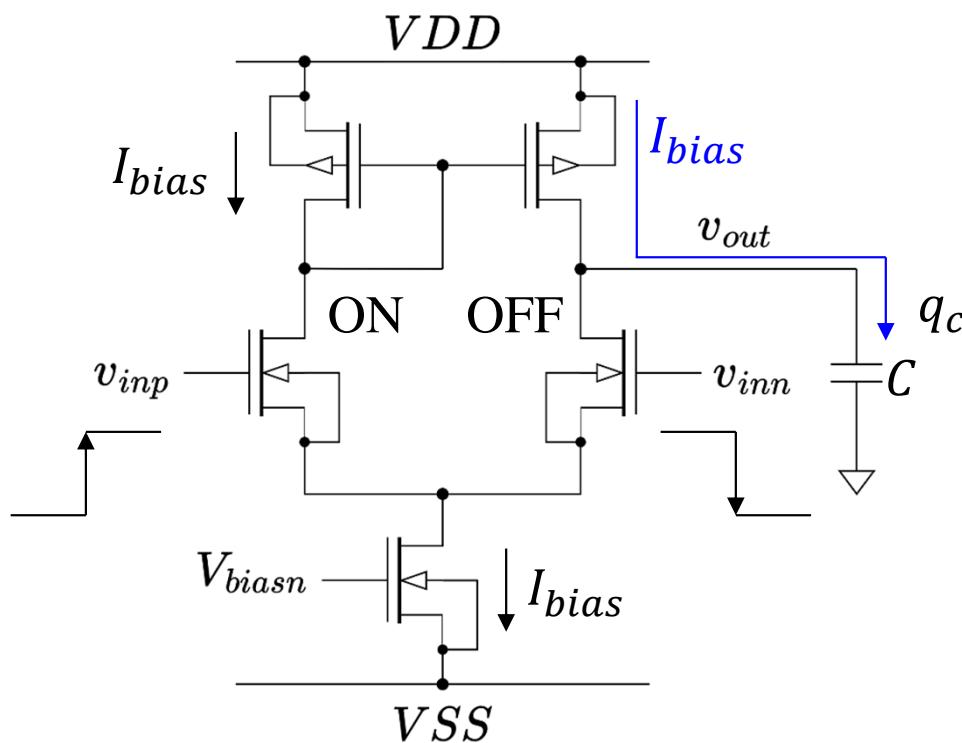

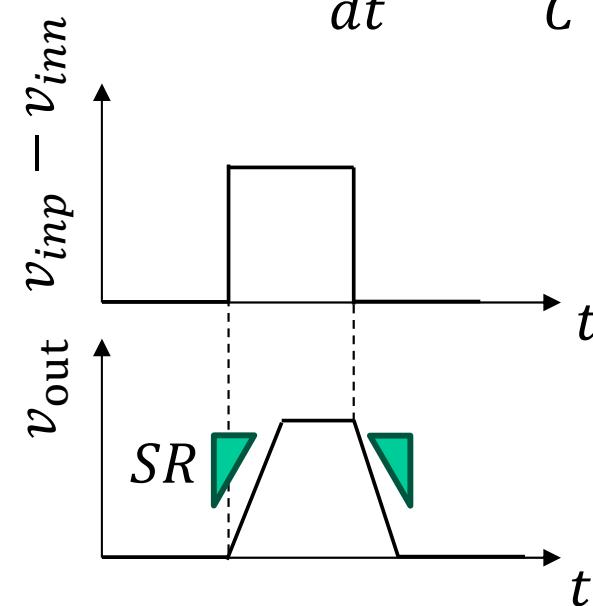

# SR(Slew rate)

M3は、同相除去の役割を持つが、一方で、ステップ応答のスピードを制限する。

$$v_{out} = \frac{q_c}{C} = \frac{I_{bias}t}{C}$$

$$SR = \frac{dv_{out}}{dt} = \frac{I_{bias}}{C}$$

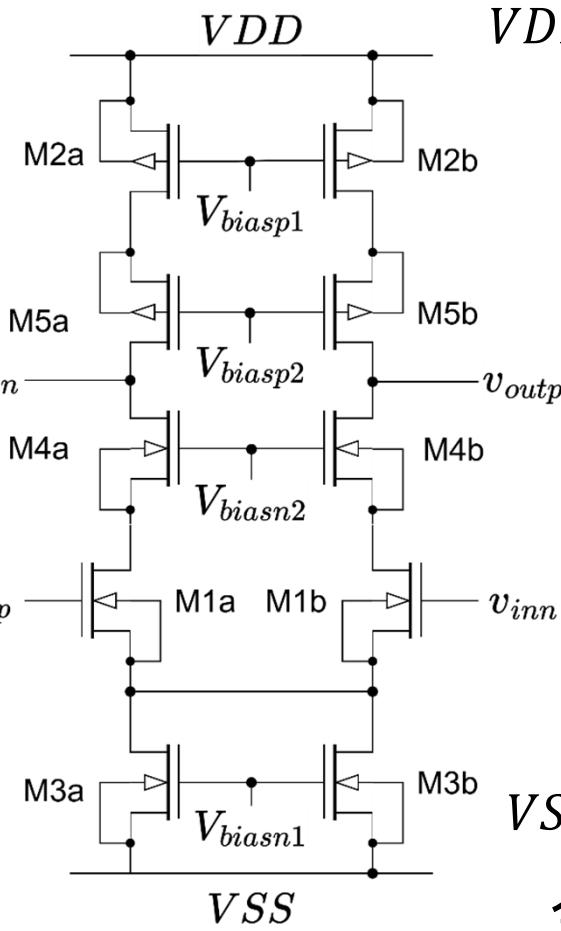

# 差動増幅回路の高利得化

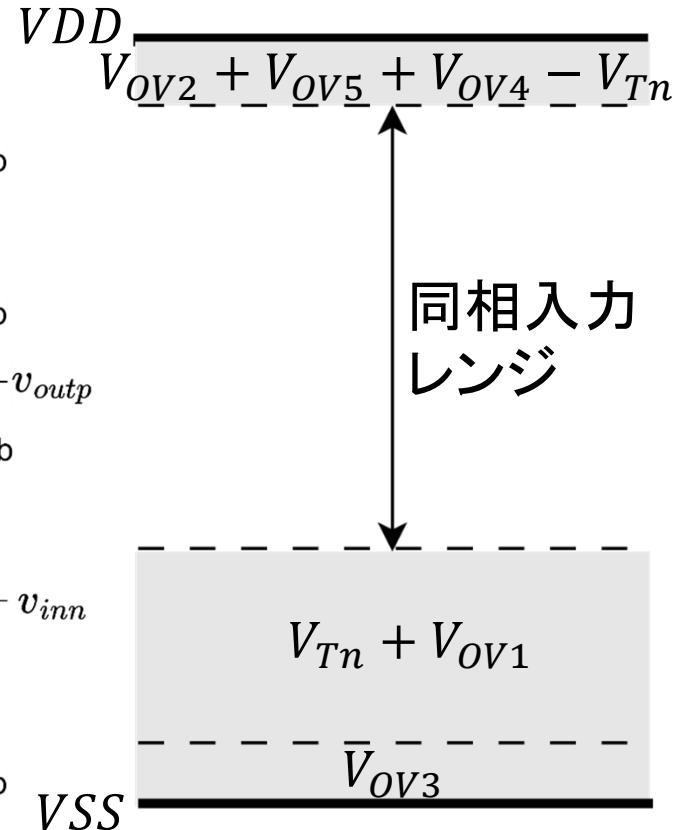

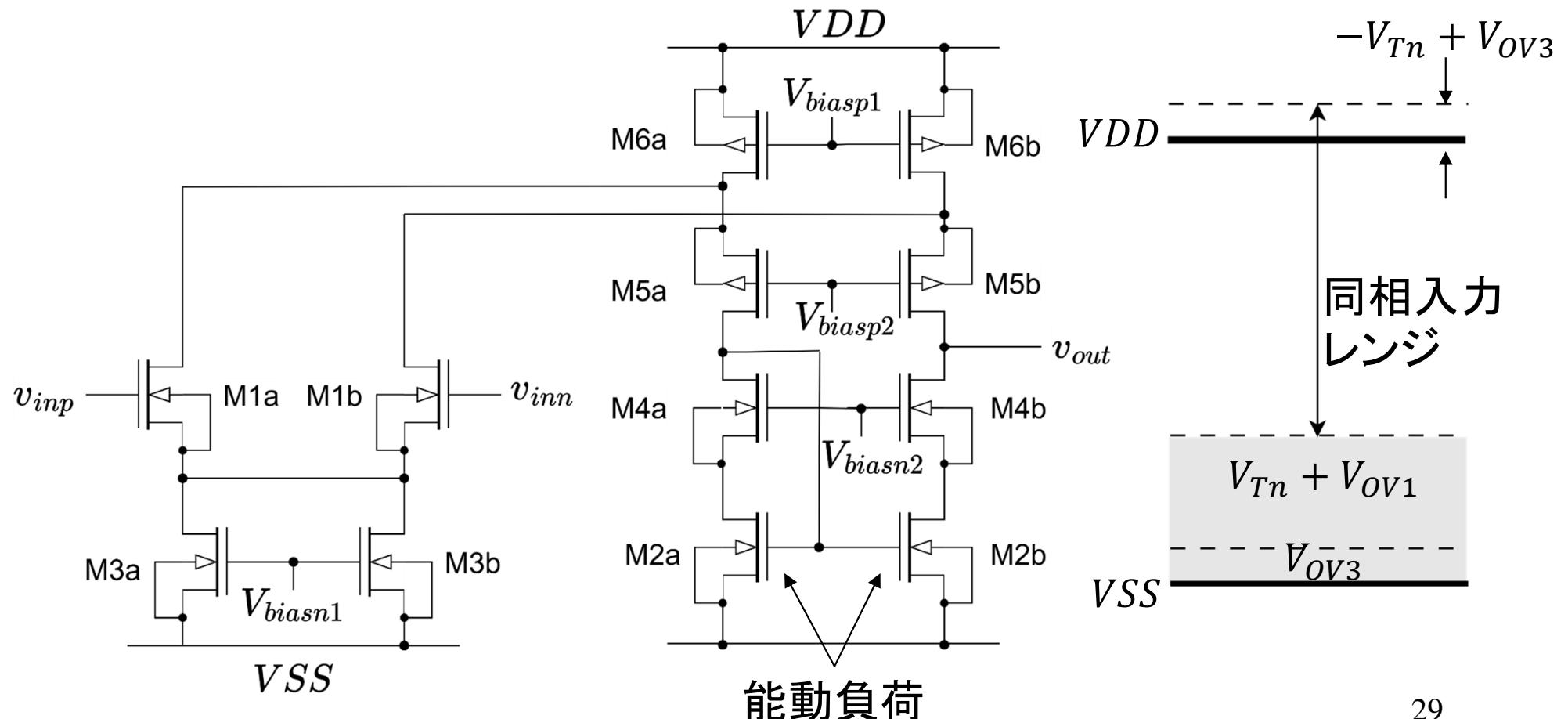

# 同相入力レンジ(Common mode input range)

前段の出力スイングよりも入力範囲が狭い

可能性があるので要注意。

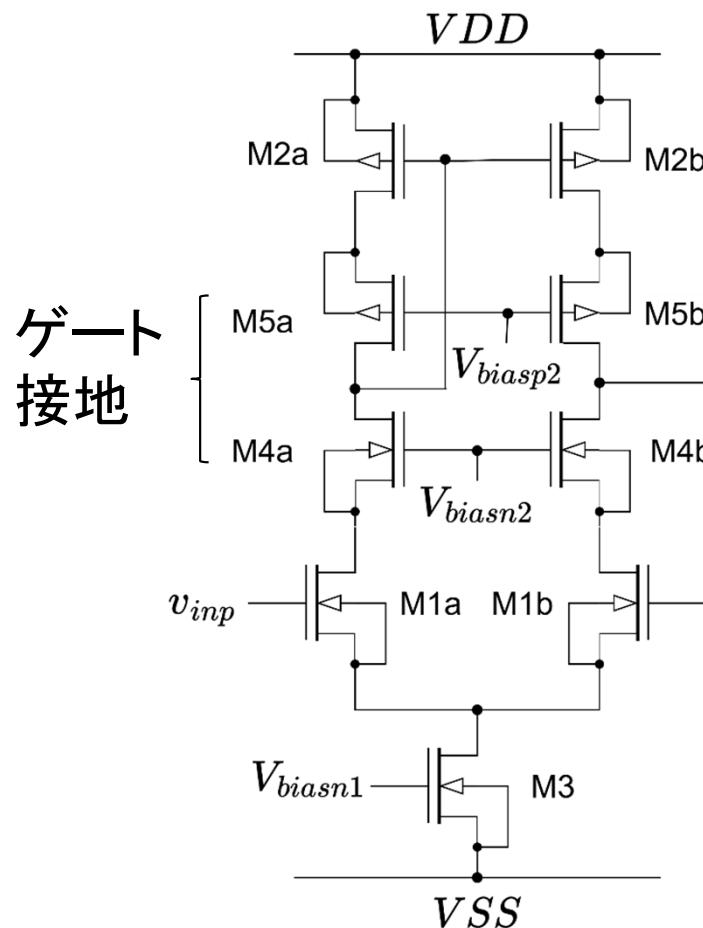

# 同相入力レンジの拡大

同相入力レンジが狭いと、事前に入力範囲を制限する必要があり使いにくい。

下記のように、差動ペアと能動負荷を分離する(Folded cascode amplifier)。

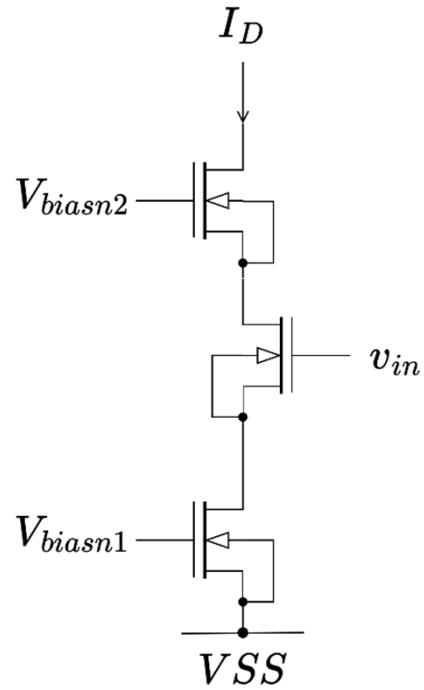

# クイズ

下記の回路について、MOSFETを飽和領域で動作させるために必要なバイアス電圧 $V_{biasn1}, V_{biasn2}$  の範囲を求めよ。全てのMOSFETのオーバードライブ電圧は $V_{OV}$ 、閾値電圧は $V_T$ とする。

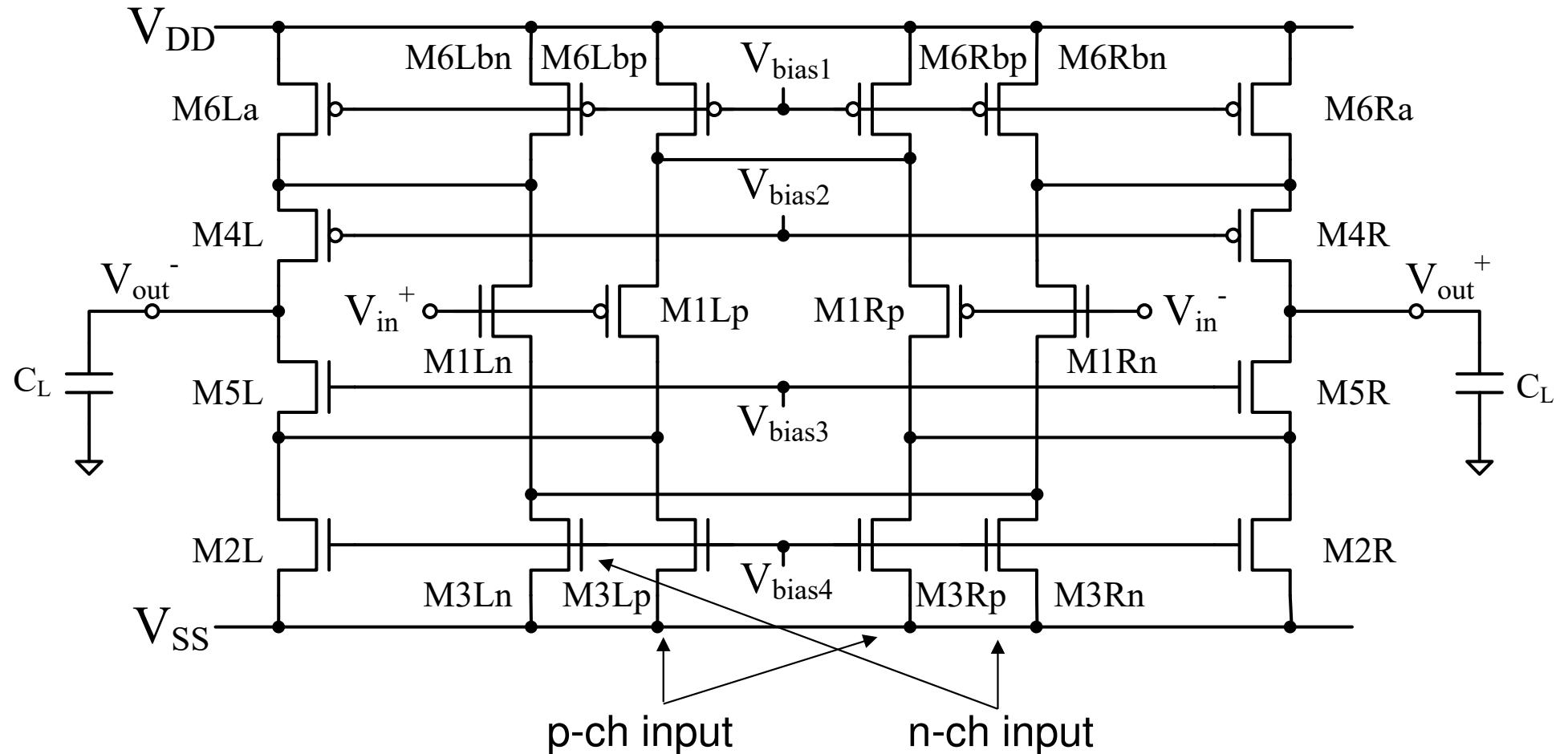

# Rail-to-Rail入力

電源よりも広い範囲で入力が可能になる。ただし、 $M1Lp$ と $M1Ln$ の  $g_m$  を入力電圧に合わせて制御する必要がある（詳細は口頭で説明）。<sub>31</sub>

# 差動増幅回路の主な性能指標

| 性能指標          | 単位                    | 説明                                |

|---------------|-----------------------|-----------------------------------|

| GBP           | Hzまたはrad/s            | 差動利得のGBP                          |

| オープンループ利得     | dB                    | 直流での差動利得                          |

| 同相除去比(CMRR)   | dB                    | 差動利得/同相利得<br>できるだけ大きいほうがよい        |

| 同相入力レンジ       | V(Max., Min.)         | 同相除去が可能な入力電圧範囲<br>Rail-to-Railが理想 |

| SR(Slew rate) | V/ $\mu$ s            | ステップ入力に対する出力電圧の時間当たりの変化           |

| 入力換算雑音レベル     | V/ $\sqrt{\text{Hz}}$ | 出力雑音/差動利得                         |

| 入力換算オフセット     | V                     | 減算誤差<br>ペアトランジスタの特性ばらつきなどが原因      |

詳細は、電子回路及び演習C,D(演算増幅器)で学ぶ。

# 第14章のまとめ

- 差動増幅回路により同相雑音や誤差を除去できる

- 差動増幅回路により基準電位を自由に設定可能

- 入力信号と出力信号の基準電位を一致させることができる

- 同相入力レンジに注意する必要がある

- 差動増幅回路には、シングルエンド型と全差動型がある

- シングルエンド型は仮想ショートを利用して基準電位を設定する

- 全差動型は、コモンモードフィードバックにより基準電位を設定する

- 差動増幅回路を高利得化するためにカスコード回路が使用される

- カスコード回路は同相入力レンジが狭くなるため、折り返しカスコードやRail-to-Rail入力回路が使用される