# 第9章 トランジスタの構造と動作 原理

Transistor = Trans + Resistor

いろいろなタイプのトランジスタと主な機能

## 9.1 トランジスタの機能

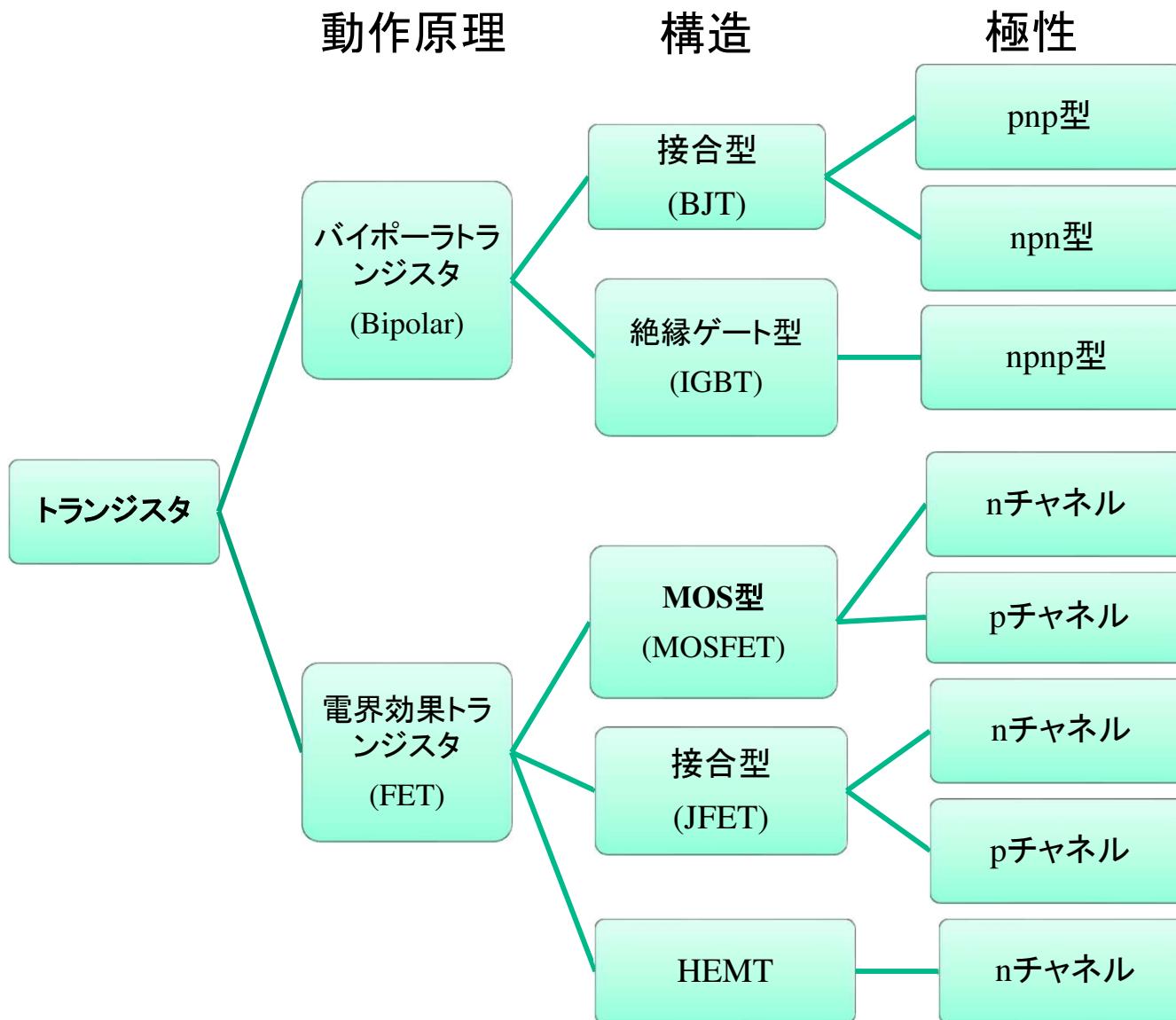

# 主なトランジスタの分類

# 各種トランジスタの特長

- 点接触トランジスタ(Point-contact Transistor)

- 発明者 John Bardeen, Walter Brattain, William B. Shockley (1956年ノーベル物理学賞受賞)

- 最初に発明されたトランジスタ(1947年), 現在は使われていない

- バイポーラ(接合形)トランジスタ(Bipolar Junction Transistor)

- 発明者 William B. Shockley

- ディスクリート回路、パワーエレクトロニクス(IGBT)で使用される

- MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)

- 発明者 Julius E. Liliendfeld(諸説ある)

- 大規模集積回路(LSI)、パワーエレクトロニクス(SiC、ダイアモンド等)で使用される

- HEMT(High Electron Mobility Transistor)

- 発明者 三村高志

- 複数の化合物半導体(人工合成した半導体)を組み合わせた構造

- 超高周波、低雑音、高耐圧などの特長をもつものがある

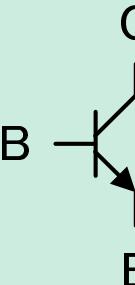

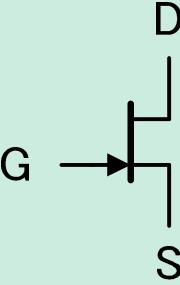

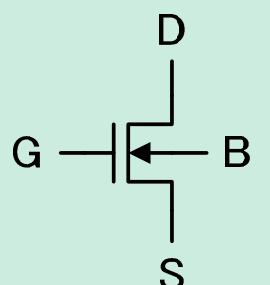

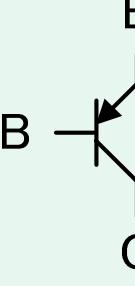

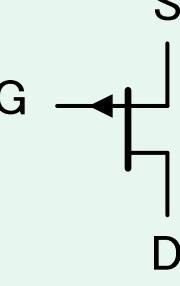

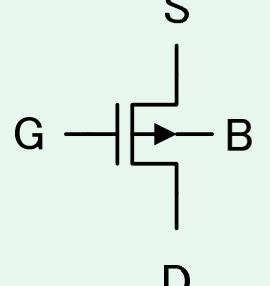

# 主なトランジスタのシンボル

| BJT                                                                                       | JFET                                                                                         | MOSFET                                                                                        |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| <br>npn  | <br>nチャネル  | <br>nチャネル  |

| <br>pnp | <br>pチャネル | <br>pチャネル |

| C: Collector<br>B: Base<br>E: Emitter                                                     | D: Drain<br>G: Gate<br>S: Source                                                             | D: Drain<br>G: Gate<br>S: Source<br>B: Body (or Bulk)                                         |

本講義ではMOSFETを使用

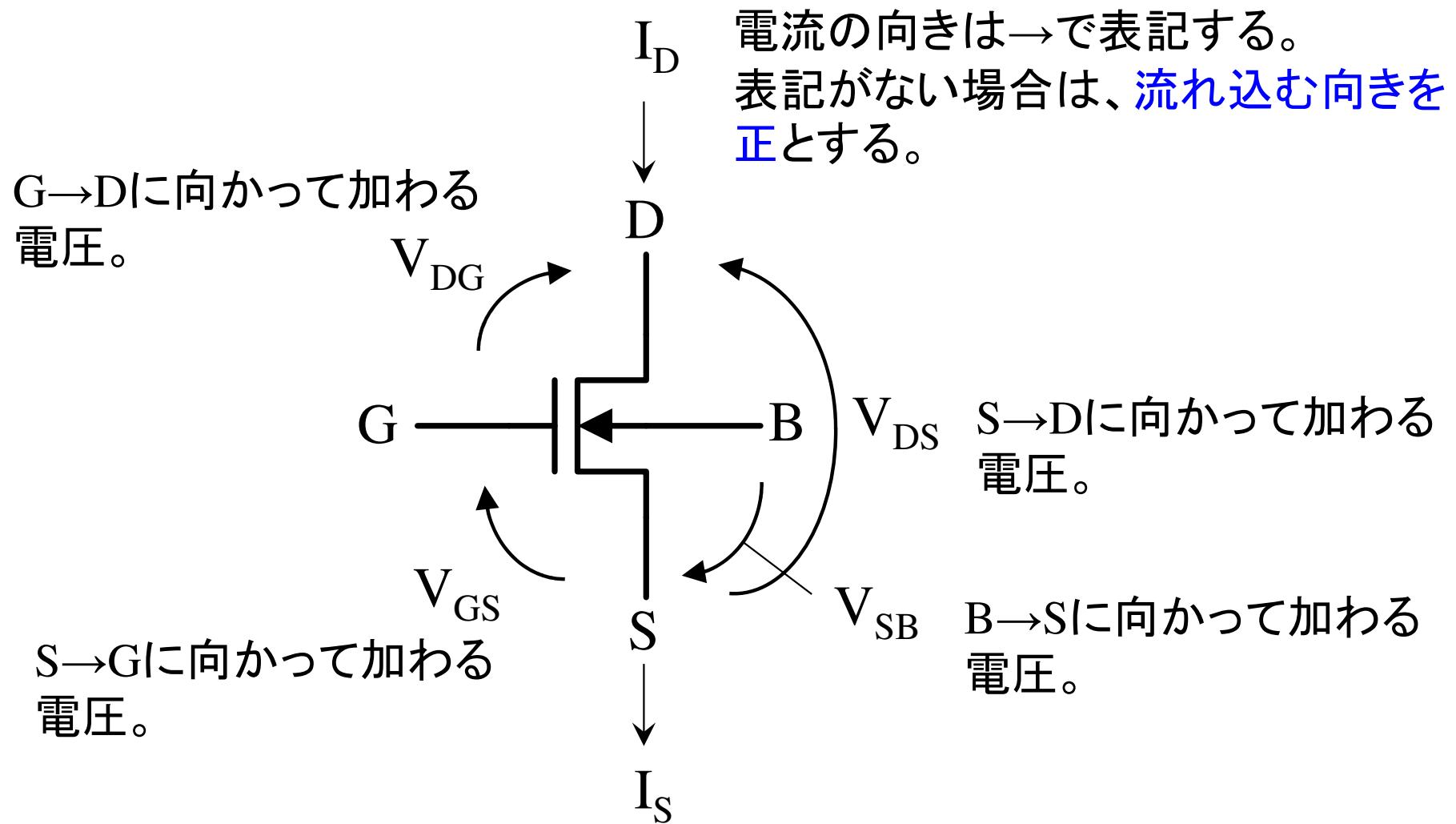

# 印加電圧と電流の表記法

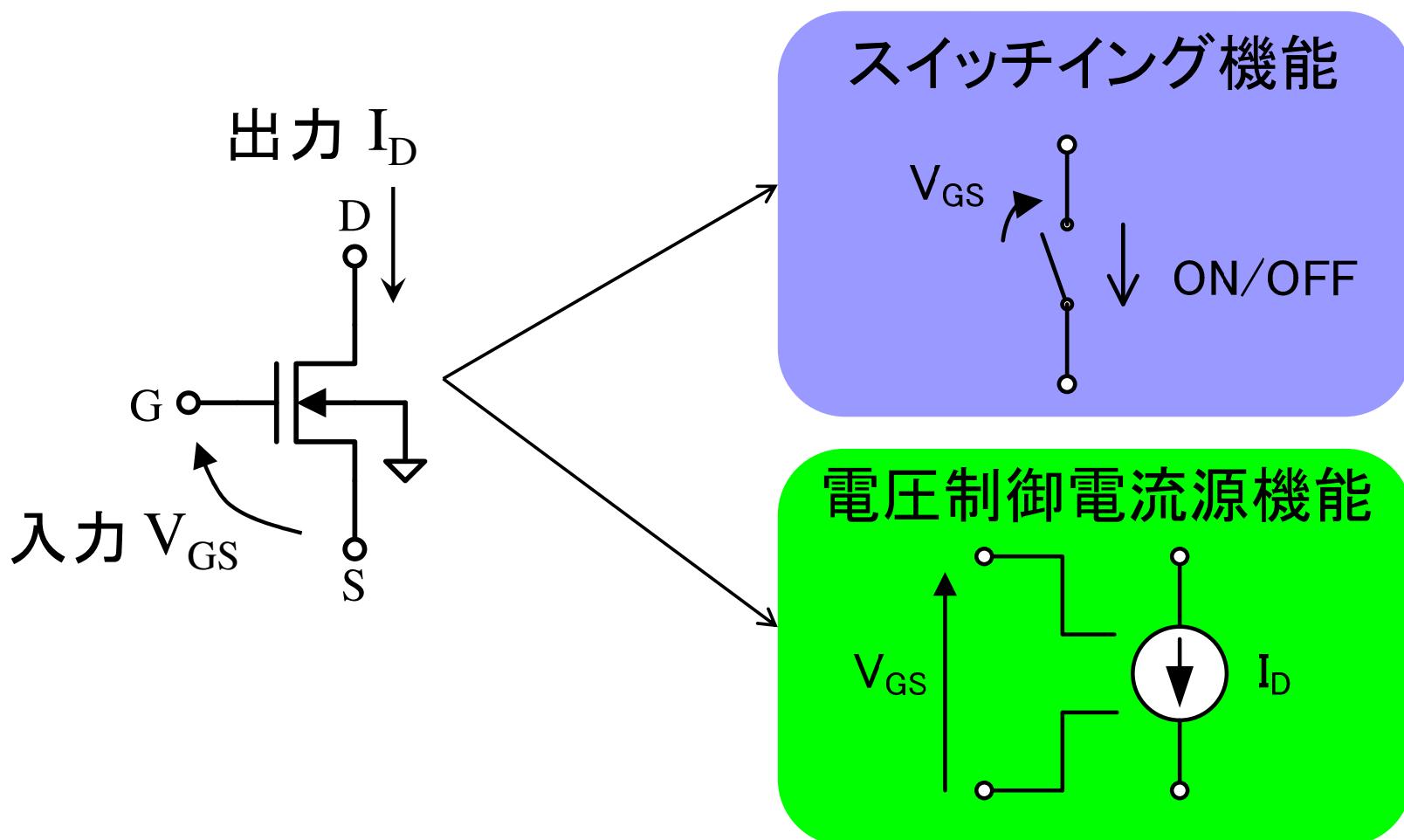

# トランジスタの2つの基本機能

いろいろな種類のトランジスタがあるが基本機能は同じ(電気的特性や性能は異なる)

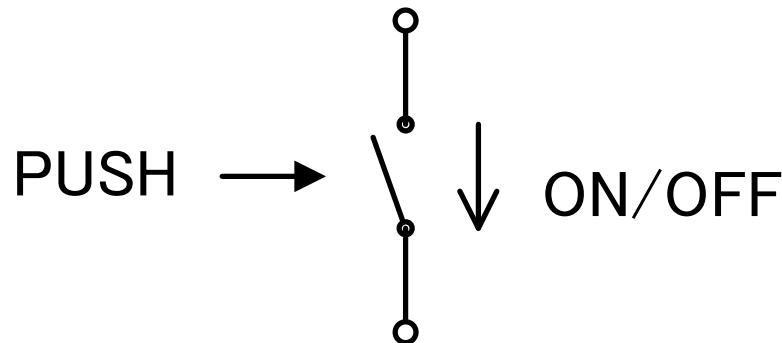

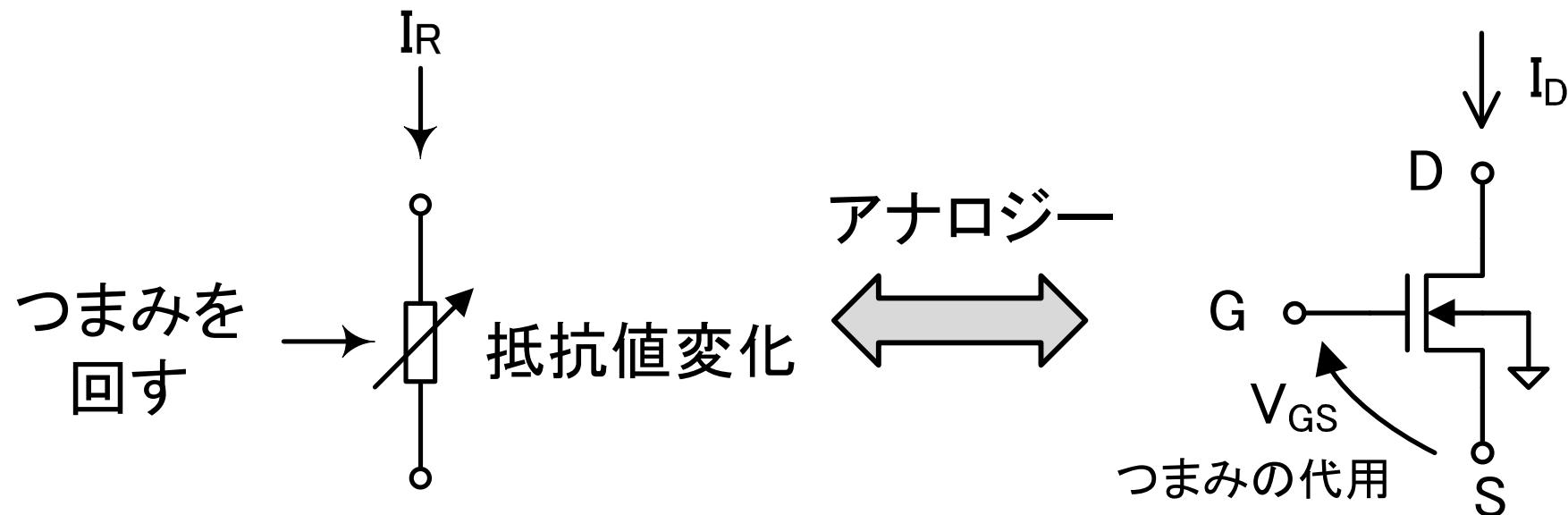

# スイッチング機能

押すと電流が流れる。

ある値以上の $V_{GS}$ を加えると電流が流れる。

アナロジー

# スイッチング機能の応用例

- 論理演算を行う

- 集積回路内のデジタル回路

- 小さな電流または電圧で大きな電流をON/OFFする

- 必要な電流の大きさやON/OFF周波数に応じて各種のトランジスタが使用される

- 複数のLEDの点灯を制御

- 7セグメントLED

- ドットマトリクスLED

- インバータ(※)

- 交流電動機(モータ)制御

- 無停電電源装置・太陽光発電(DC-AC変換)

- 蛍光灯、液晶ディスプレイのバックライトの高周波点灯

- 電子レンジ、電磁加熱調理器

※ 論理回路のNOTゲートのことではなく、DC-AC変換による電力制御回路を指す。

AC電力に変換することで直流よりも電力利用効率が高い電源回路が作れる。

# 電圧制御電流源機能

つまみを回すと電流が増える。

$V_{GS}$ を増やすと電流が増える。

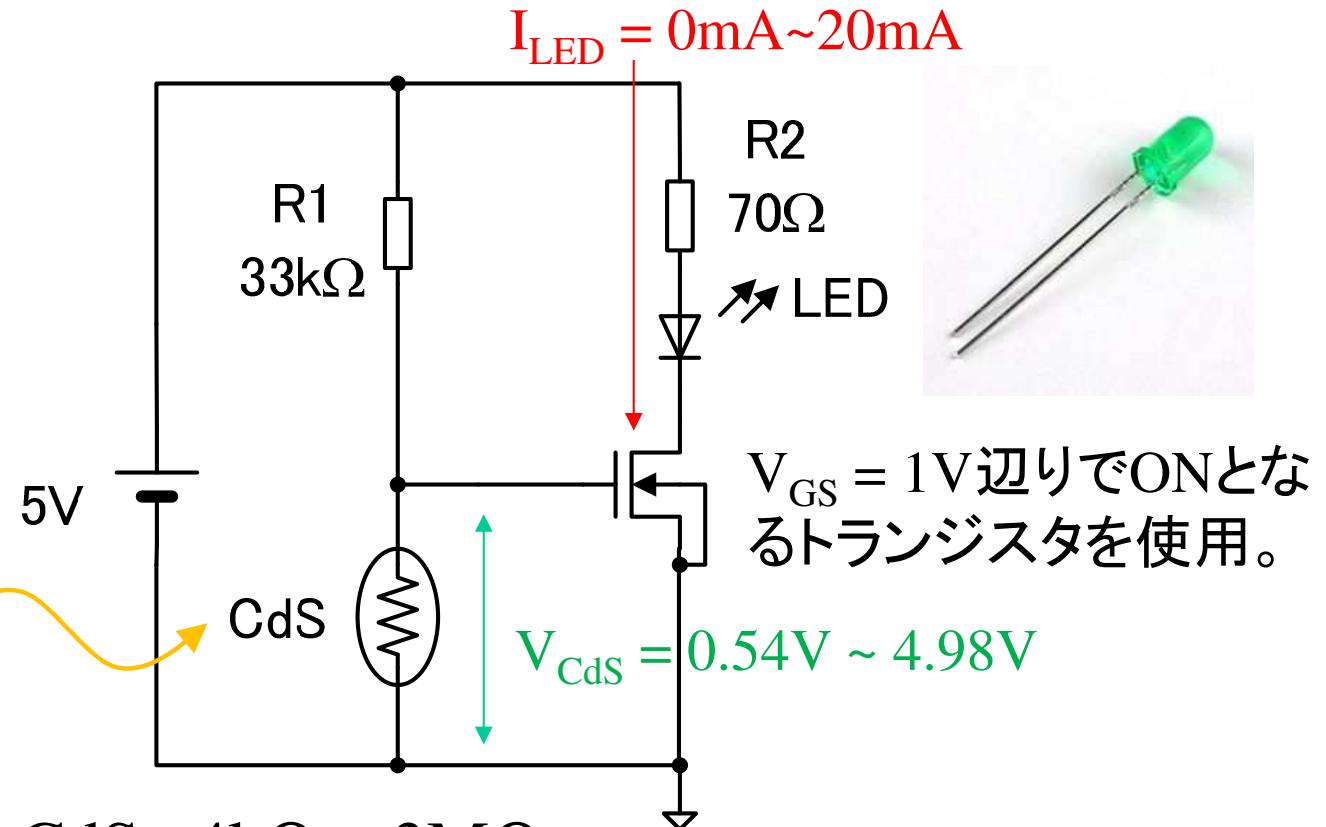

# 電圧制御電流制御機能の応用例

光を照射すると抵抗が下がる。

光 : 1000lx ~ 1lx → CdS :  $4\text{k}\Omega \sim 3\text{M}\Omega$

$$\rightarrow V_{Cds} = V_{GS} = 0.54\text{V(OFF)} \sim 4.98\text{V(ON)}$$

暗いほど  $V_{CDS}$  が高くなつて、LED(Light Emitting Diode)が明るく光る。

# 9.1節のまとめ

- トランジスタの分類

- 動作原理の違いによりBJTとFETの2種類に分けられる

- FETは構造の違いによりJFET, MOSFET, HEMTなどに分けられる

- トランジスタの電極

- BJTの電極は、Collector, Base, Emitter

- JFETの電極は、Drain, Gate, Source

- MOSFETの電極は、Drain, Gate, Source, Body

- トランジスタの電圧は $V_{GS}$ (ソースからゲートに加わる電圧)のように端子名を付けた変数で表される

- トランジスタの機能

- スイッチング

- 電圧制御電流源

半導体の電流方向制御機能

## 9.2 PN接合

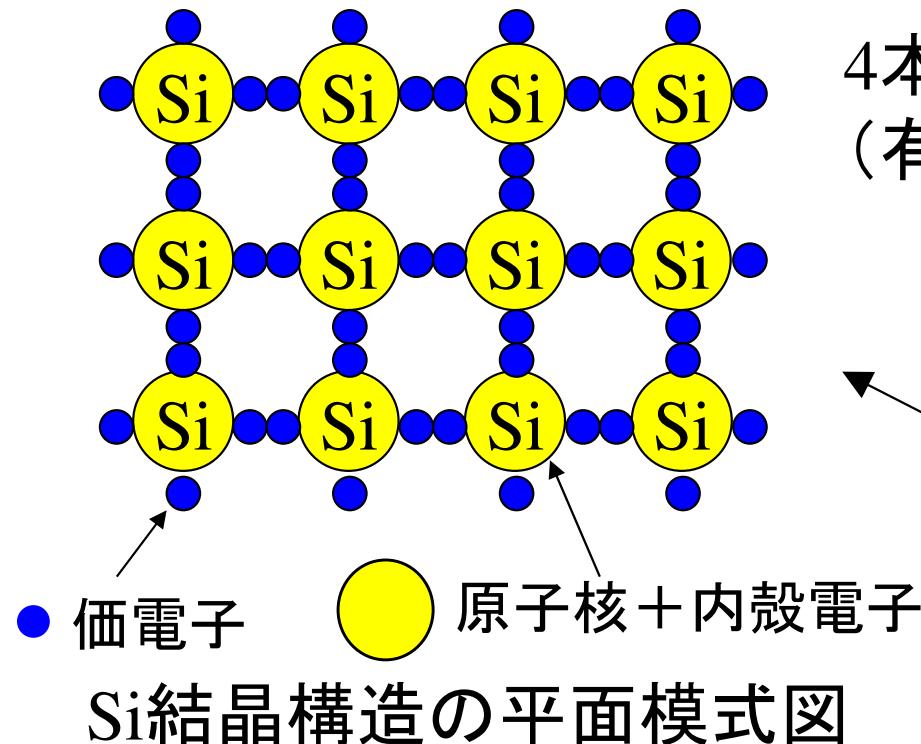

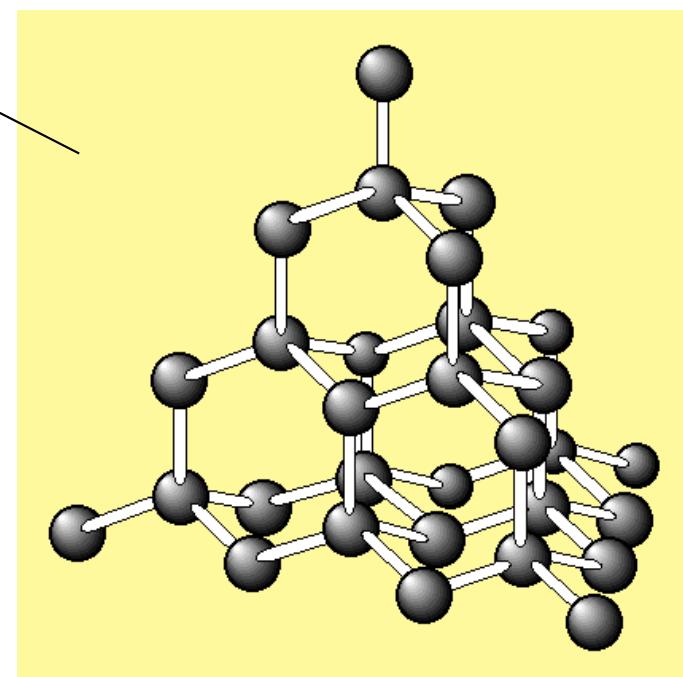

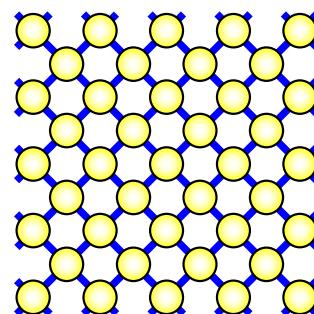

# 結晶シリコン(Crystalline Silicon)

4本の結合手で共有結合している。

(有機物に多い結合メカニズム)

実際には正四面体を積み上げたダイヤモンド構造をしている。

共有結合している電子は移動することができない。→

シリコン自体は絶縁体と同じ。

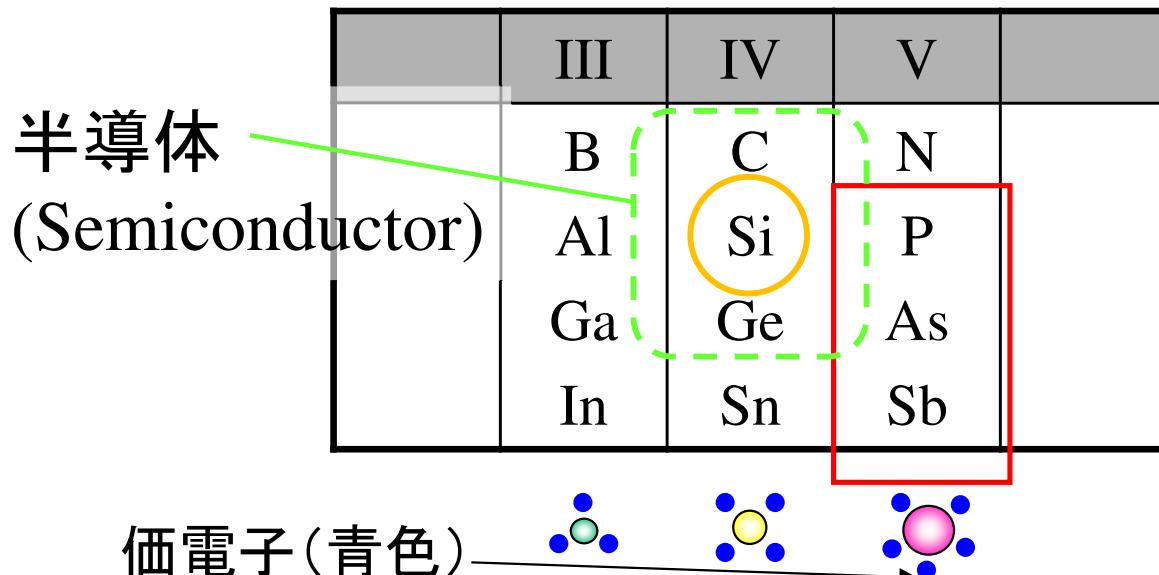

# 不純物による電気伝導の制御1

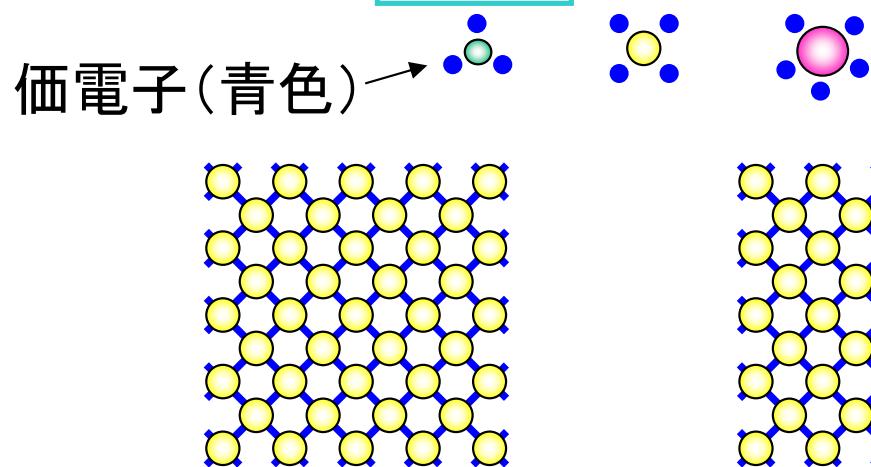

※ 結合電子と区別するため移動できる電子は自由電子と呼ばれる。以後、省略して単に「電子」と呼ぶ。

自由電子: Free Electron (結合に関与しない価電子) ※

Siの結晶の模式図

P(リン)ドープSi結晶

簡略表示

ドープ(Dope): 不純物を混ぜること

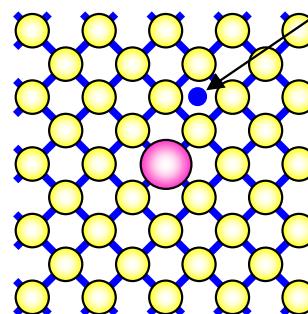

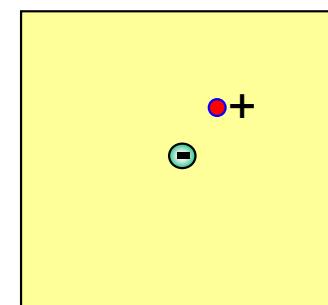

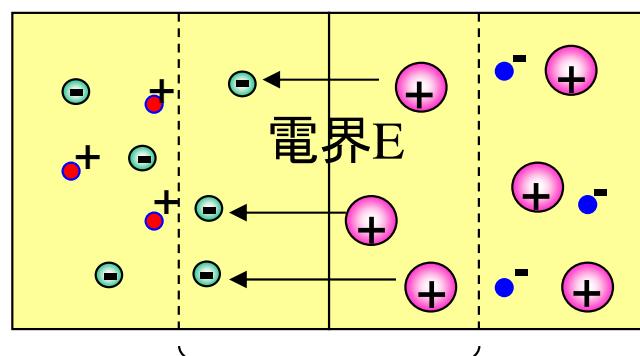

# 不純物による電気伝導の制御2

|  | III | IV | V  |  |

|--|-----|----|----|--|

|  | B   | C  | N  |  |

|  | Al  | Si | P  |  |

|  | Ga  | Ge | As |  |

|  | In  | Sn | Sb |  |

B(ボロン)ドープSi結晶

ドープ(Dope):不純物を混ぜること

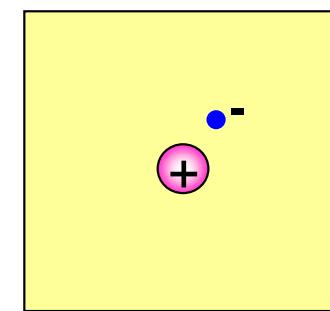

※ ボロンの周辺のシリコン原子が電子を奪われて+にイオン化した状態だが、+の場所は移動できるので(シリコンは移動しない)、+が単体で移動していると見做す。

ホール: hole(結合手の電子が不足してできた孔)※

簡略表示

# 不純物による電気伝導の制御3

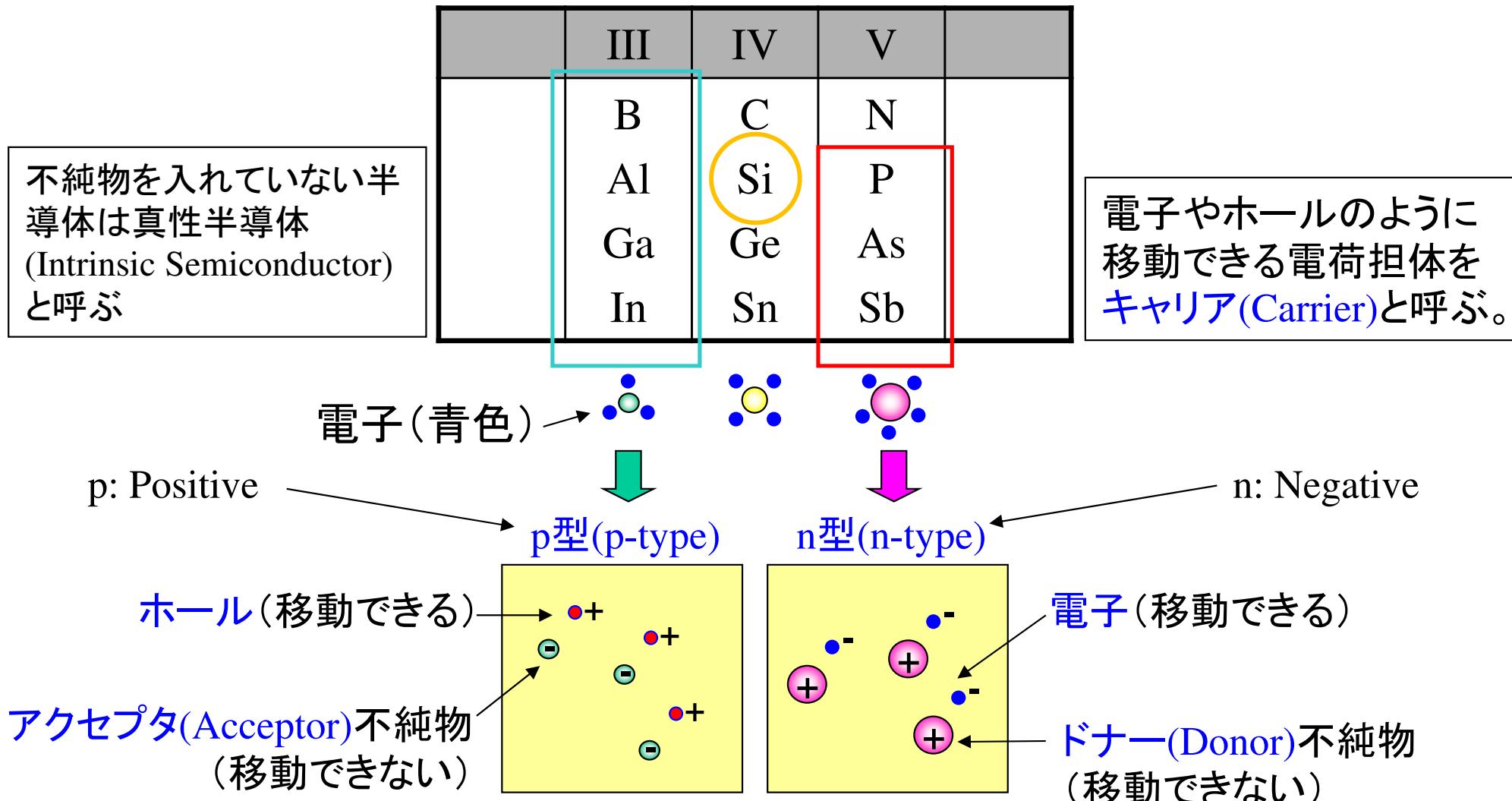

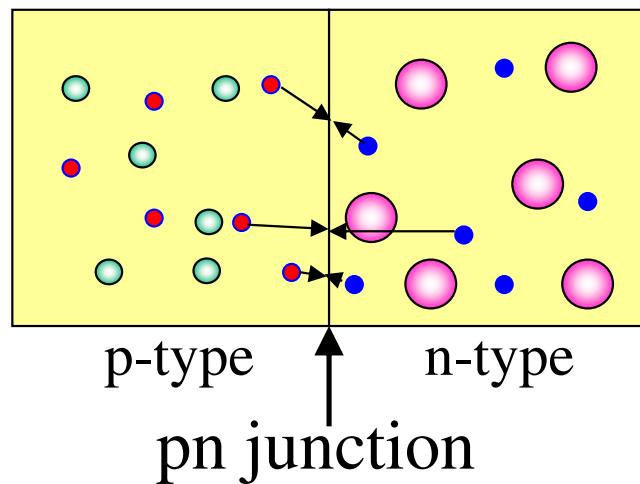

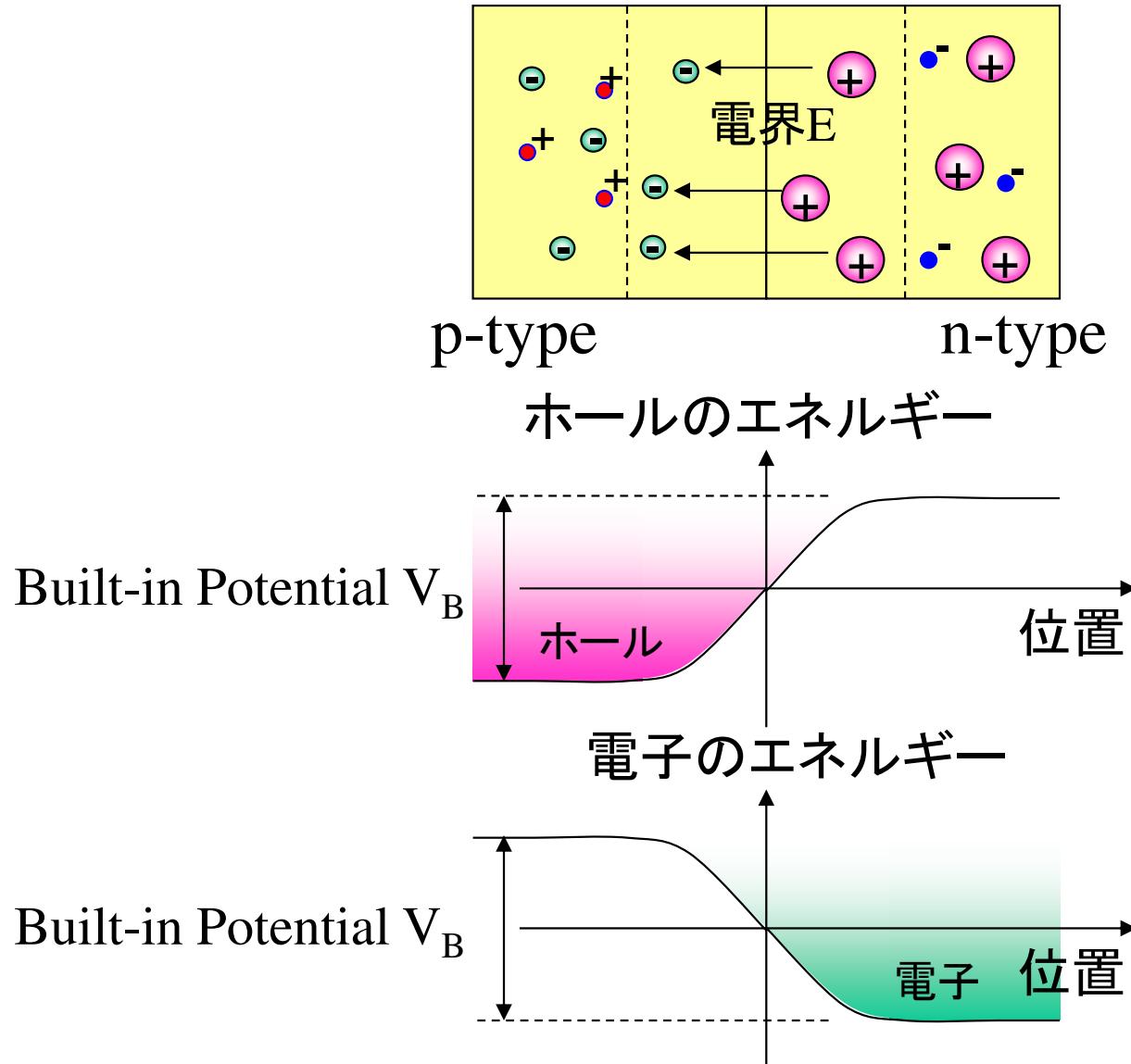

# pn接合の構造 1

p型領域とn型領域が接したところをpn接合(pn junction)と呼ぶ。

pn接合の付近では、電子とホールがぶつかって再結合する(自由電子がホールを埋めて消える)。

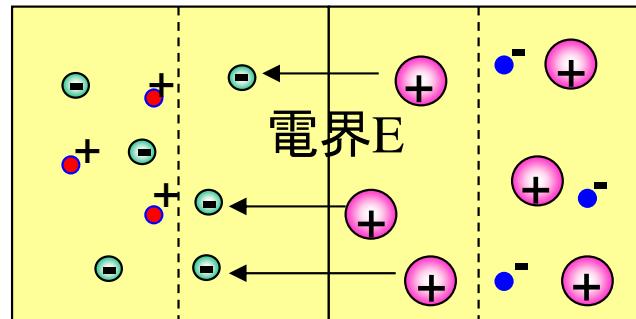

電荷を持ったアクセプタとドナーが残るので内部電界Eが発生。

$$\frac{dE}{dx} = \frac{\rho}{\epsilon_0 \epsilon_{Si}} \quad (\text{ガウスの法則})$$

電子とホールが再結合した領域(空乏層, Depletion layer)

# pn接合の構造2

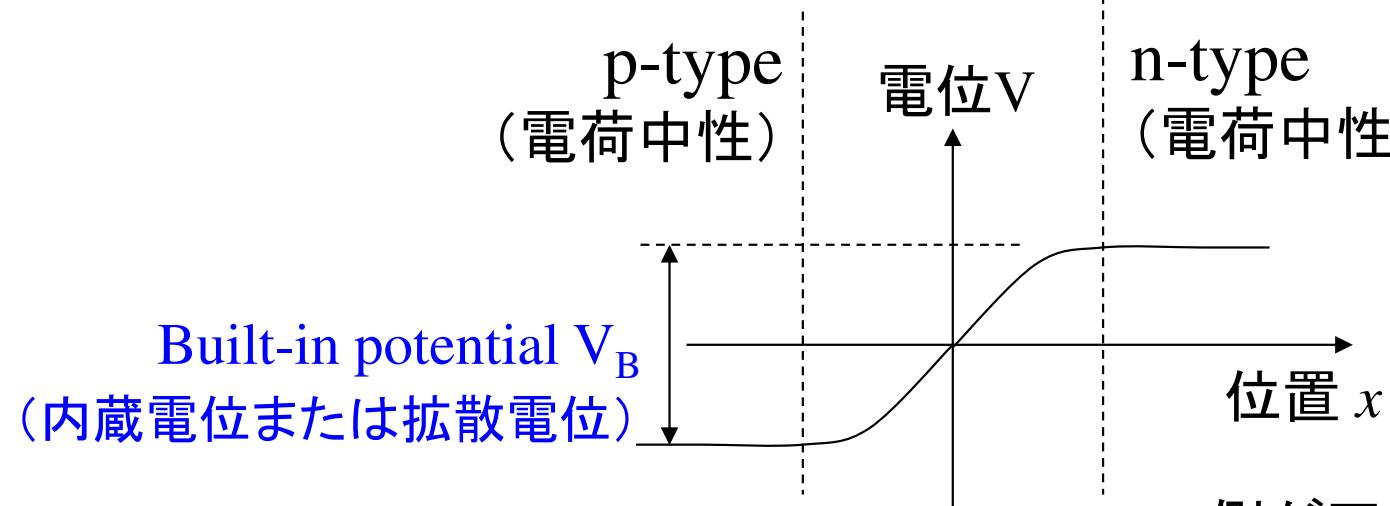

内部電界が発生したので、内部電位 $V_B$ が発生。

$$E = -\frac{dV}{dx}$$

$$dV = -Edx$$

$$V_B = \int dV = - \int E dx$$

n-type側が正電位になる。

但し、電流は流れない。

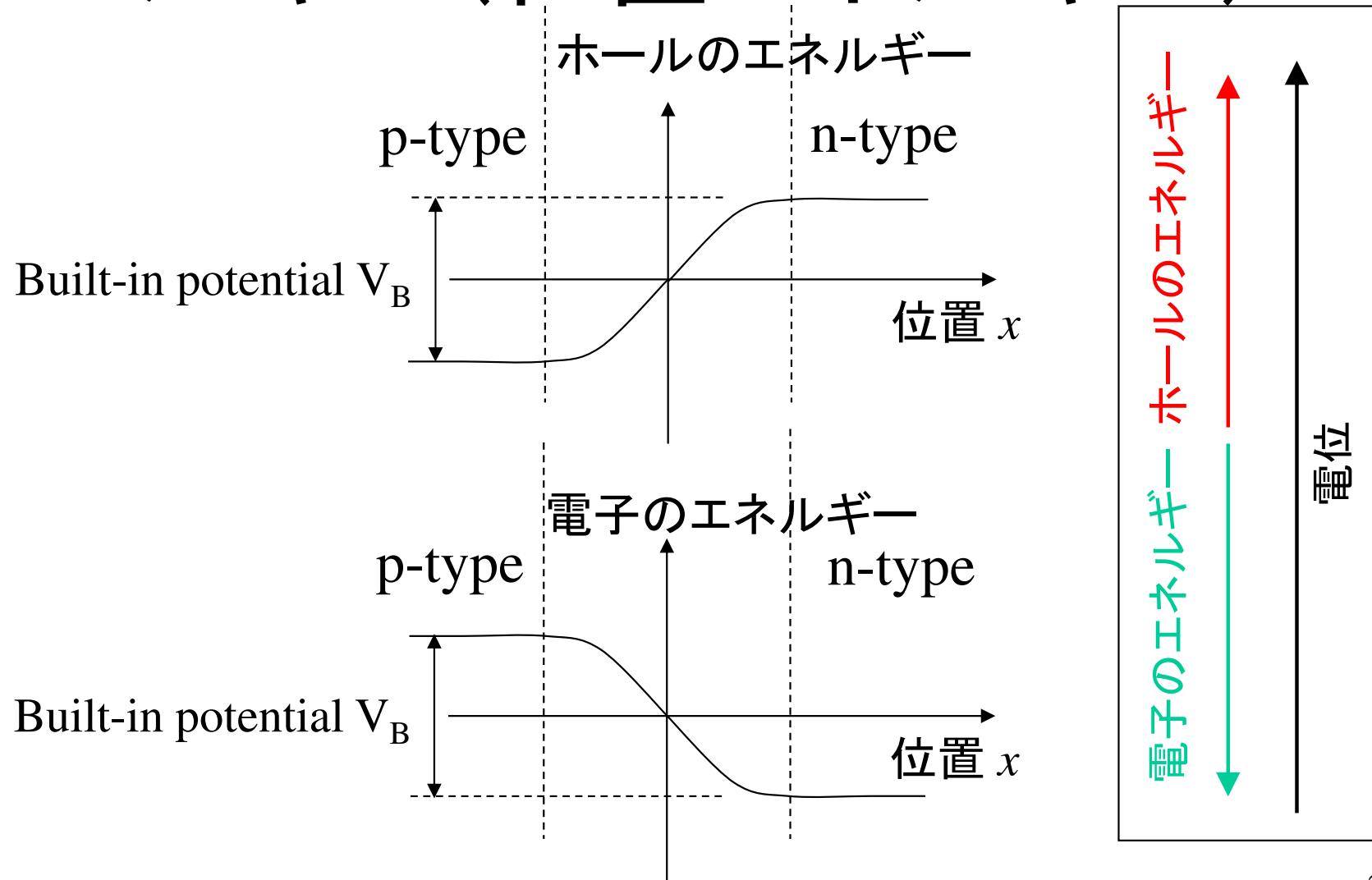

# 電子とホールのポテンシャルエネルギー(位置エネルギー)

# 自由電子とホールの分布

室温(300K)では、キャリアは、ポテンシャルエネルギーの低い領域に溜まっている。

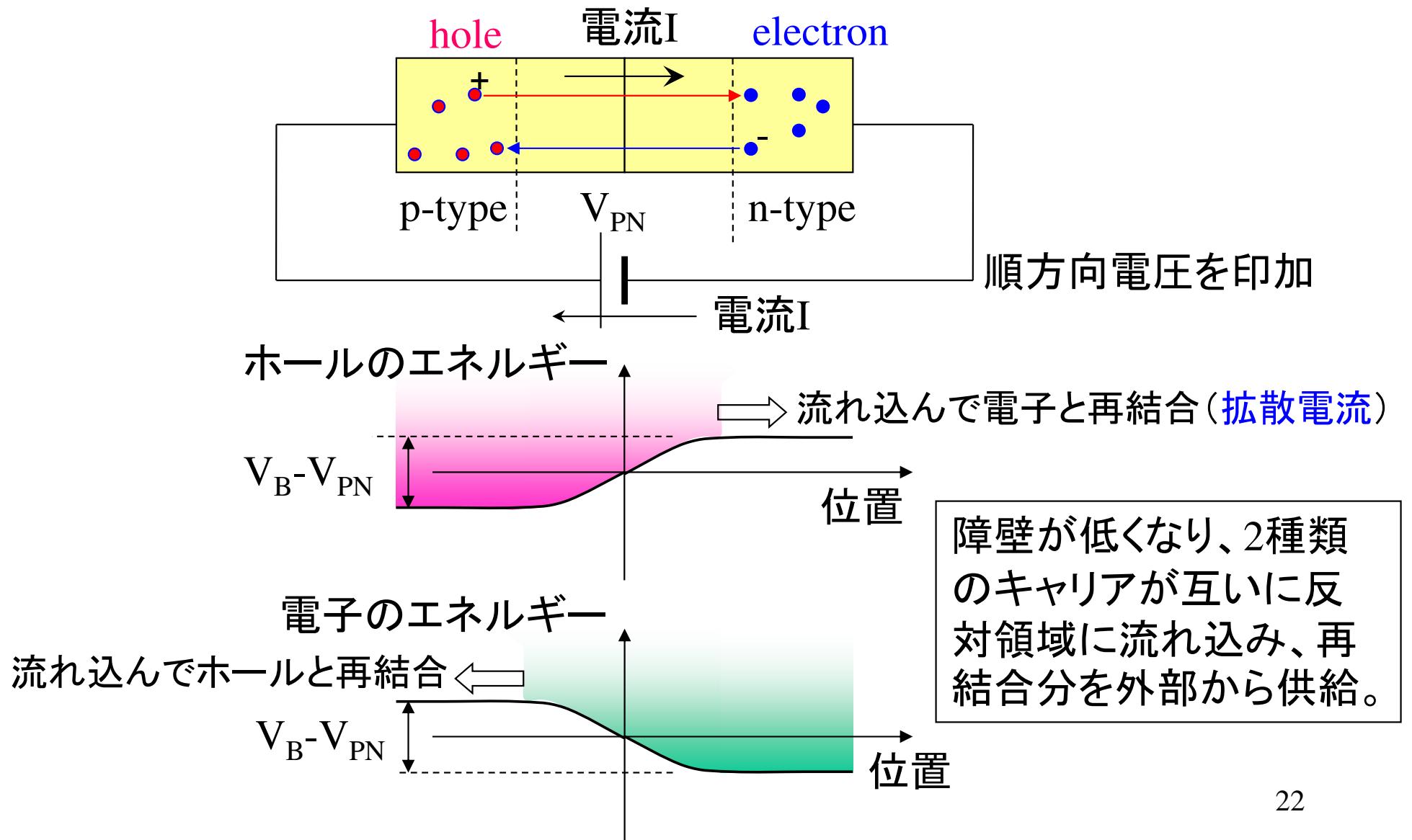

# pn接合のDC特性(順方向)

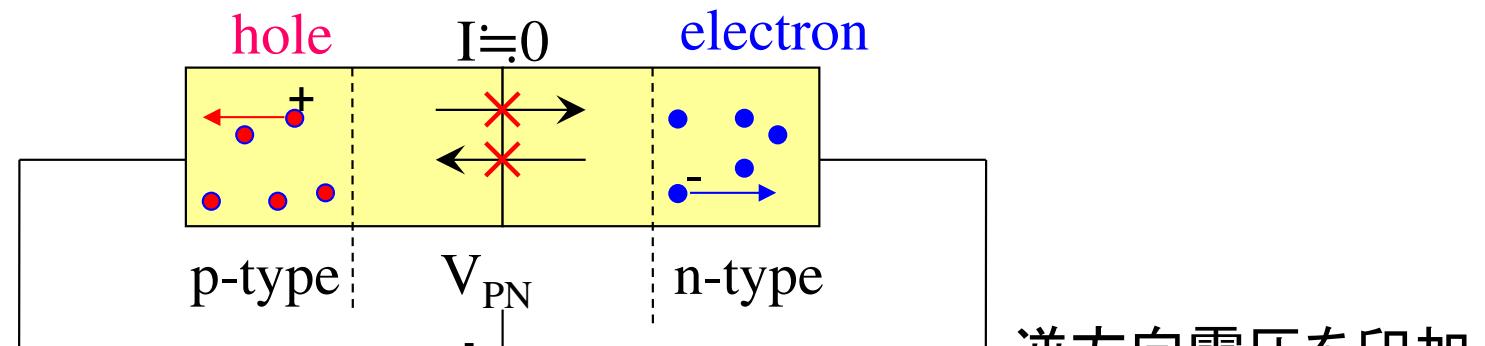

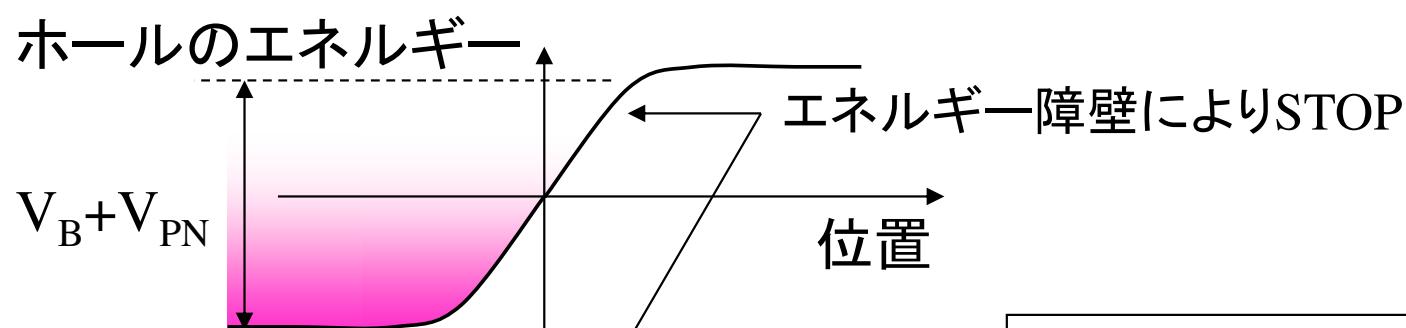

# pn接合のDC特性(逆方向)

逆方向電圧を印加

障壁が高くなり、キャリアが移動できない。

## 9.2節のまとめ

- IV族元素のC, Si, Geの結晶は半導体(Semiconductor)の物性を示す

- (参考) III族-V族元素の組み合わせや、II族-VI族元素の組み合わせでも半導体になる(LEDやHEMT)

- 半導体を構成するIV族元素は、結合手で結びついた共有結合をしており、基本的に絶縁体と同じ電子構造である

- 半導体は不純物のドープ(Dope)により電気伝導性を持つ

- 不純物ドープしていない半導体は真性半導体(Intrinsic Semiconductor)

- III族不純物をドープした半導体はp型半導体(P-type semiconductor)

- V族不純物をドープした半導体はn型半導体(N-type semiconductor)

- 電子(Electron)とホール(Hole)をまとめてキャリア(Carrier)と呼ぶ

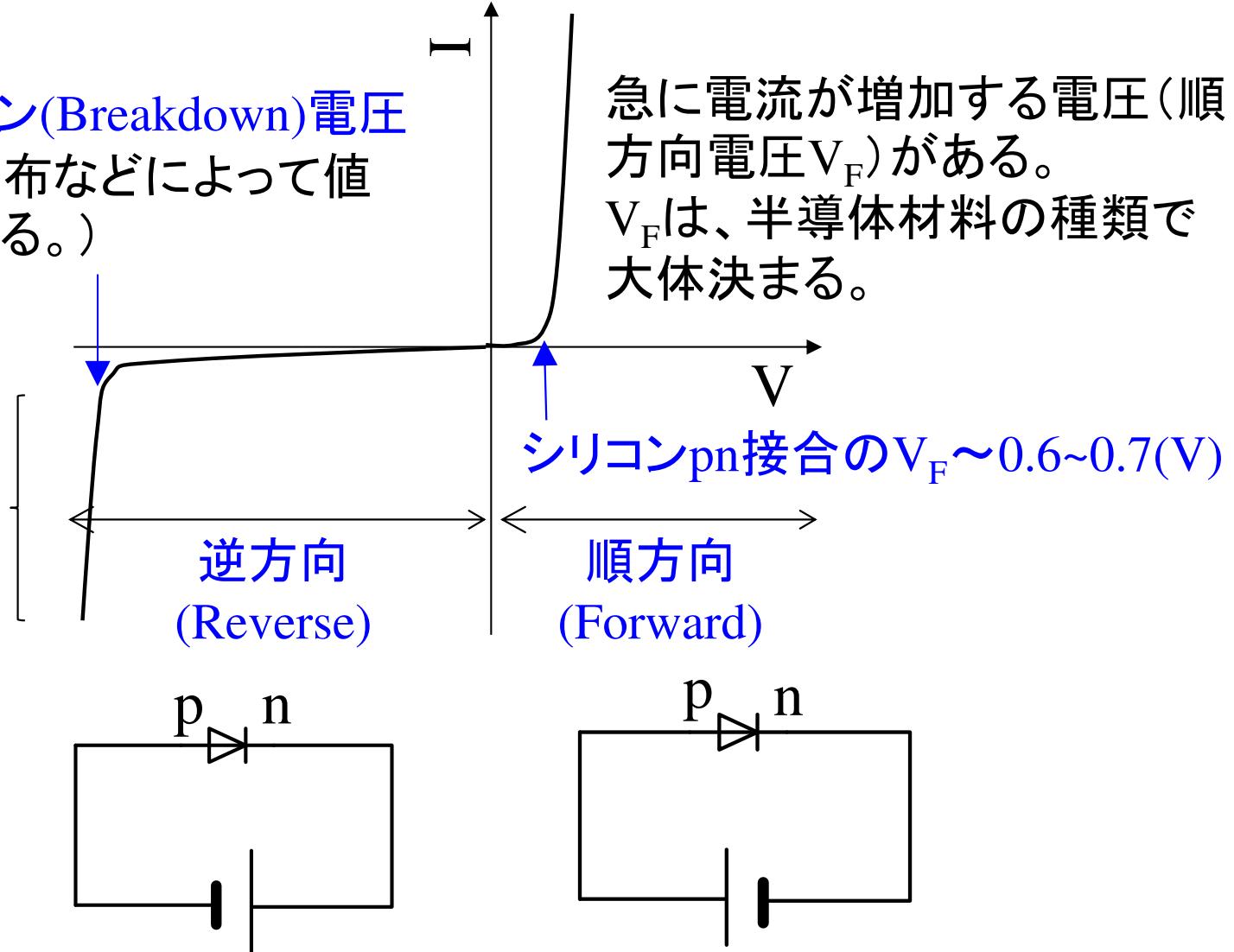

- pn接合は一方向にだけ電流を流す

- p型半導体とn型半導体の接合面をpn接合(pn junction)と呼ぶ

- pn接合には内部電位(Built-in potential)が発生する

- p型半導体にはホール(Hole)、n型半導体には自由電子(Free electron)が集まっているが、順方向電圧を印加すると移動して電流になる

最もシンプルな半導体デバイス

**9.3 ダイオード**

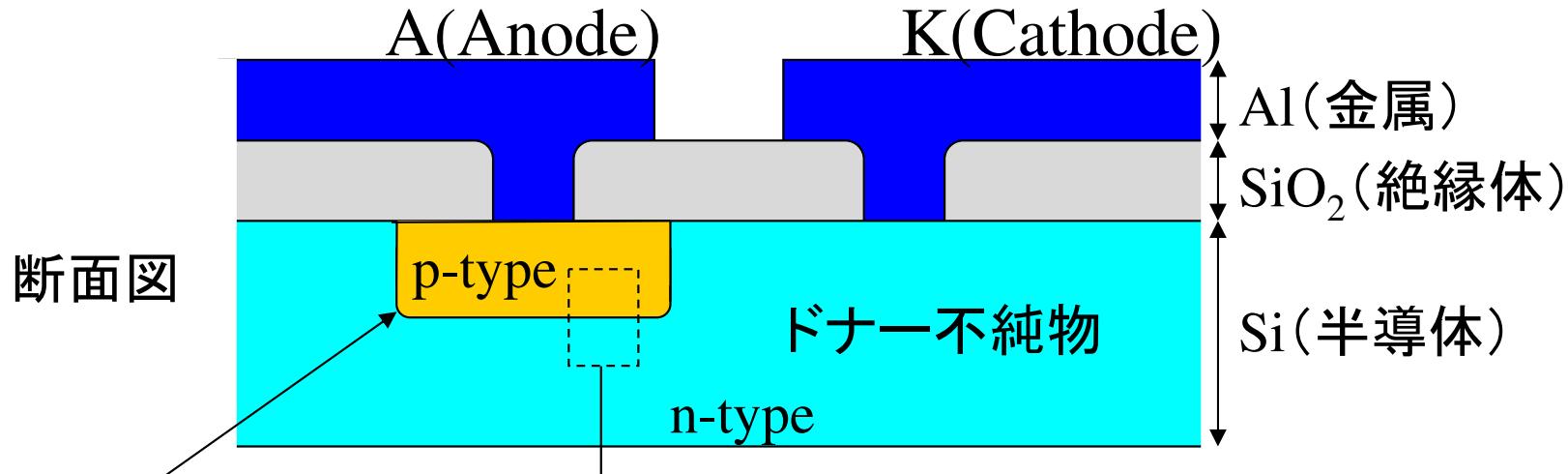

# ダイオードの構造

p型領域とn型領域が接したところ=pn接合

部分的にアクセプタ不純物を導入。

pn接合の模式図

A (Anode)

Symbol

K (Cathode) (Kはドイツ語由来?)

ダイオードの本体はpn接合(pn junction)。

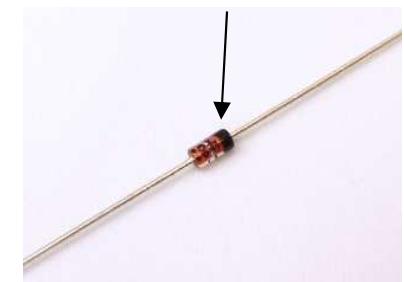

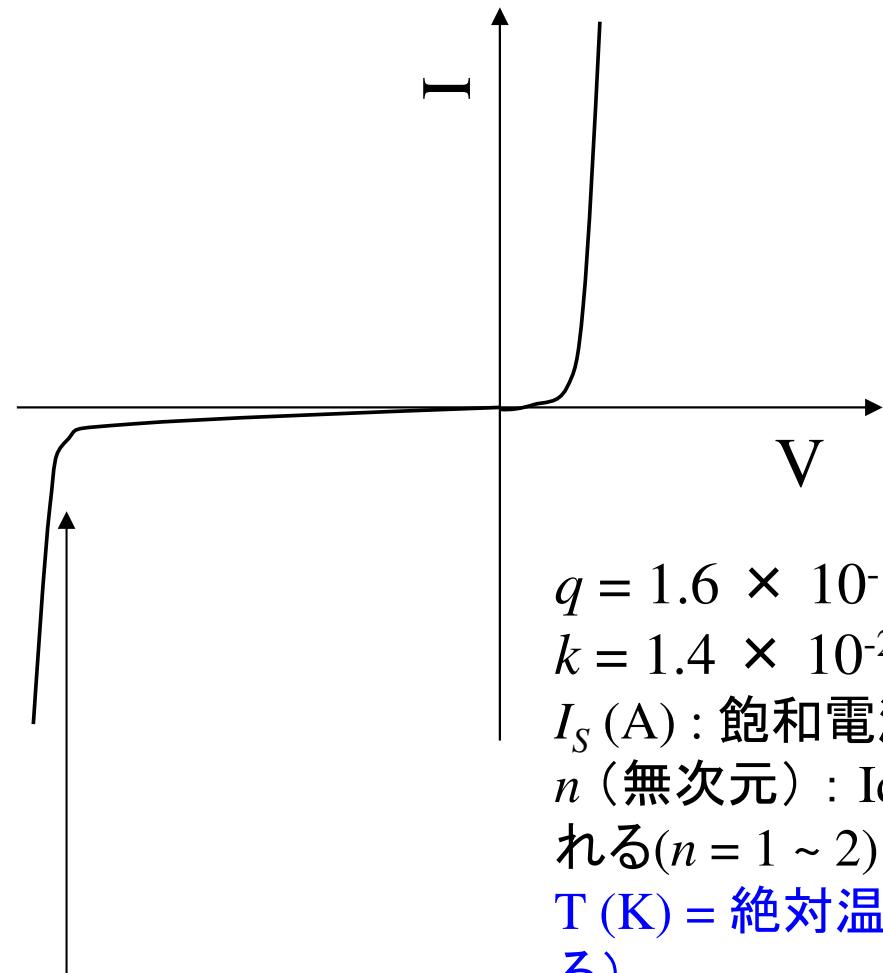

# ダイオードのDC特性

ブレークダウン(Breakdown)電圧

(不純物の分布などによって値

が大きく変わる。)

pn接合に強

電界を加える

と、急に発生

電流が増大

する(ブレー

クダウンのメ

カニズムの説

明は省略)。

# ダイオードの直流電流モデル式

理論的に求められる拡散電流

と発生電流の式

$$I = I_S \left( e^{\frac{qV}{nkT}} - 1 \right)$$

$q = 1.6 \times 10^{-19}$  (クーロン) : 電子の電荷(電気素量)

$k = 1.4 \times 10^{-23}$  (J/K) : ボルツマン定数

$I_S$  (A) : 飽和電流と呼ばれる(pn接合の面積や温度で決まる)

$n$  (無次元) : Ideality factor またはEmission coefficientと呼ばれる( $n = 1 \sim 2$ )

T (K) = 絶対温度(ダイオードの特性は強い温度依存性がある)

ブレークダウン(Breakdown)現象は、上の式では表せないが、回路シミュレータでは、ブレークダウンを計算できる精密なモデル式が使用されている。

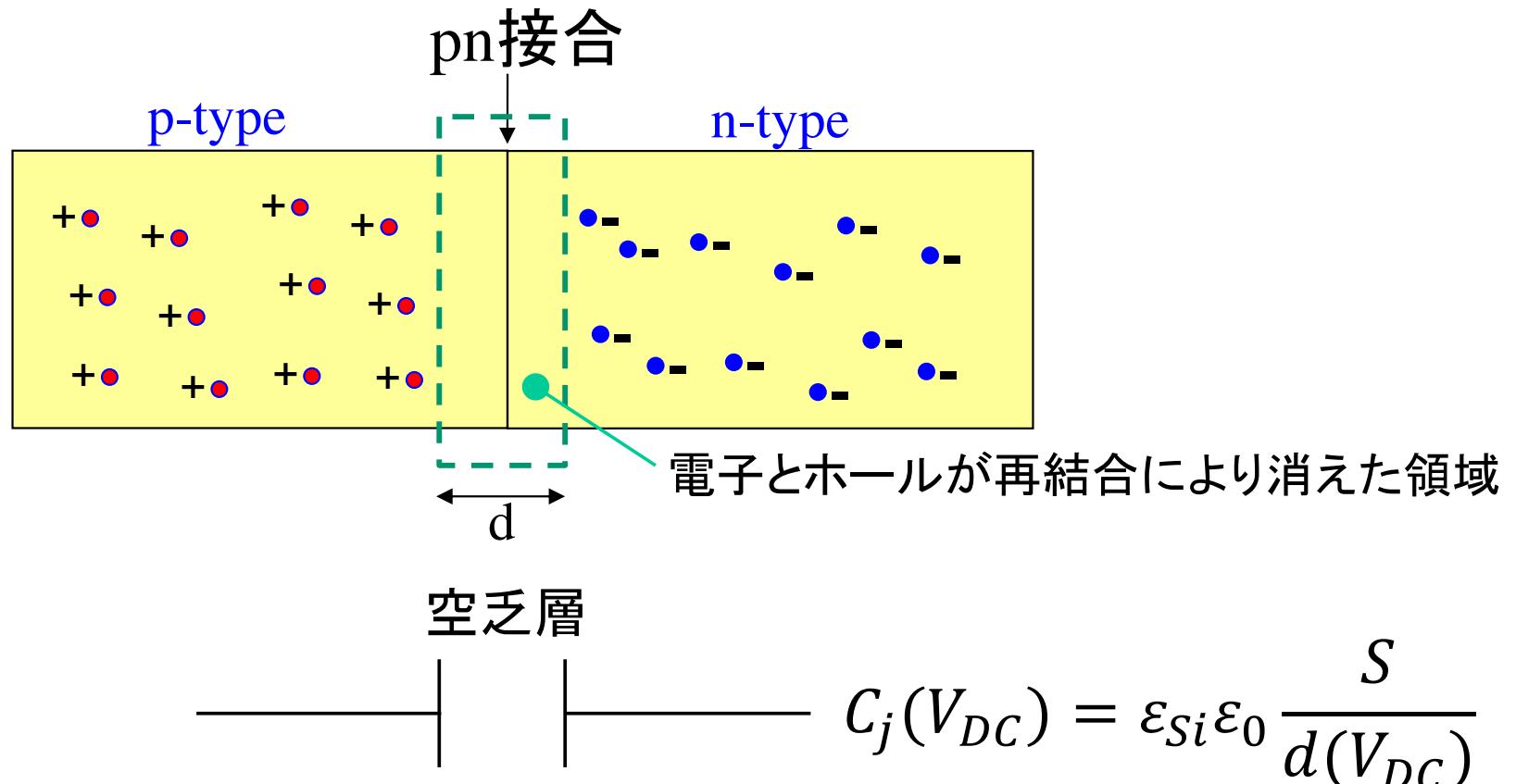

# ダイオードのAC特性

空乏層(Depletion layer)は、電子とホールがほとんど無いため、絶縁体と同じ性質を持っている。このためpn接合は、並行平板キャパシタと等価である。ただし、空乏層幅dは印加した直流電圧に依存するので、直流電圧によって変化するキャパシタンス(可変容量、Variable capacitance)となる。

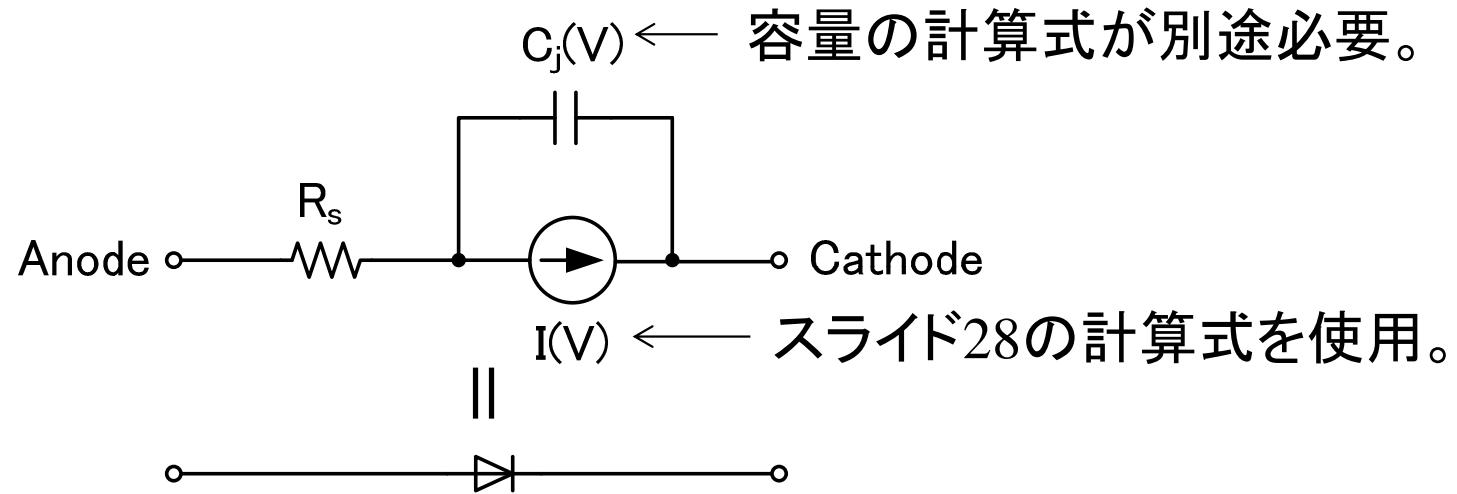

# ダイオードのシミュレーションモデル

ダイオードは、シミュレータの中では、電流-電圧の関係式 $I(V)$ , 容量-電圧の関係式 $C_j(V)$ , 半導体や電極の直列抵抗 $R_s$ でモデル化されている。その他の半導体デバイスも、同様の考え方で、**デバイスモデル**(※)が作られている。

※ デバイスモデル=デバイスの特性を求める計算式。また、デバイスモデルの中で使用されている定数がデバイスモデルパラメータである。デバイスモデルパラメータの値は、デバイスの各部寸法および実測した電気的特性から推定される。

# 9.3節のまとめ

- ダイオード(pn接合)のDC特性

- 順方向電圧を印加すると電流が流れ、シリコンダイオードでは、0.6V付近で急激に電流が大きくなる

- 逆方向電圧を印加するとごく僅かに電流が流れるが順方向電流に比べて非常に小さい

- 順方向と逆方向の電流-電圧特性をまとめて、指数関数で表すことができる

- 逆方向にブレークダウン電圧(Breakdown voltage)以上の電圧を印加すると急に大電流が流れ始める(ブレークダウン電圧は、数V～数100V程度)

- ダイオードのAC特性

- 交流に対してキャパシタの性質を持つ

- 直流電圧によりキャパシタンスが変化する(可変容量)

- DC特性とAC特性の計算式を組み合わせてデバイスマodelが構成される

- デバイスマodelに含まれるデバイスマodelパラメータの値は、デバイスの寸法および実測した電気的特性から推定される

電子回路を構成する最も基本的なデバイス

## 9.4 MOSFETの構造と動作原理

# MOSFETの語源

- MOS構造を持ち電界で電流を制御するタイプのトランジスタ

- M = Metal (金属、Poly-Siやシリサイドなど)

- O = Oxide (酸化物、 $\text{SiO}_2$ など)

- S = Semiconductor (半導体、シリコンなど)

- F = Field (電界)

- E = Effect (効果)

- T = Transistor (トランジスタ)

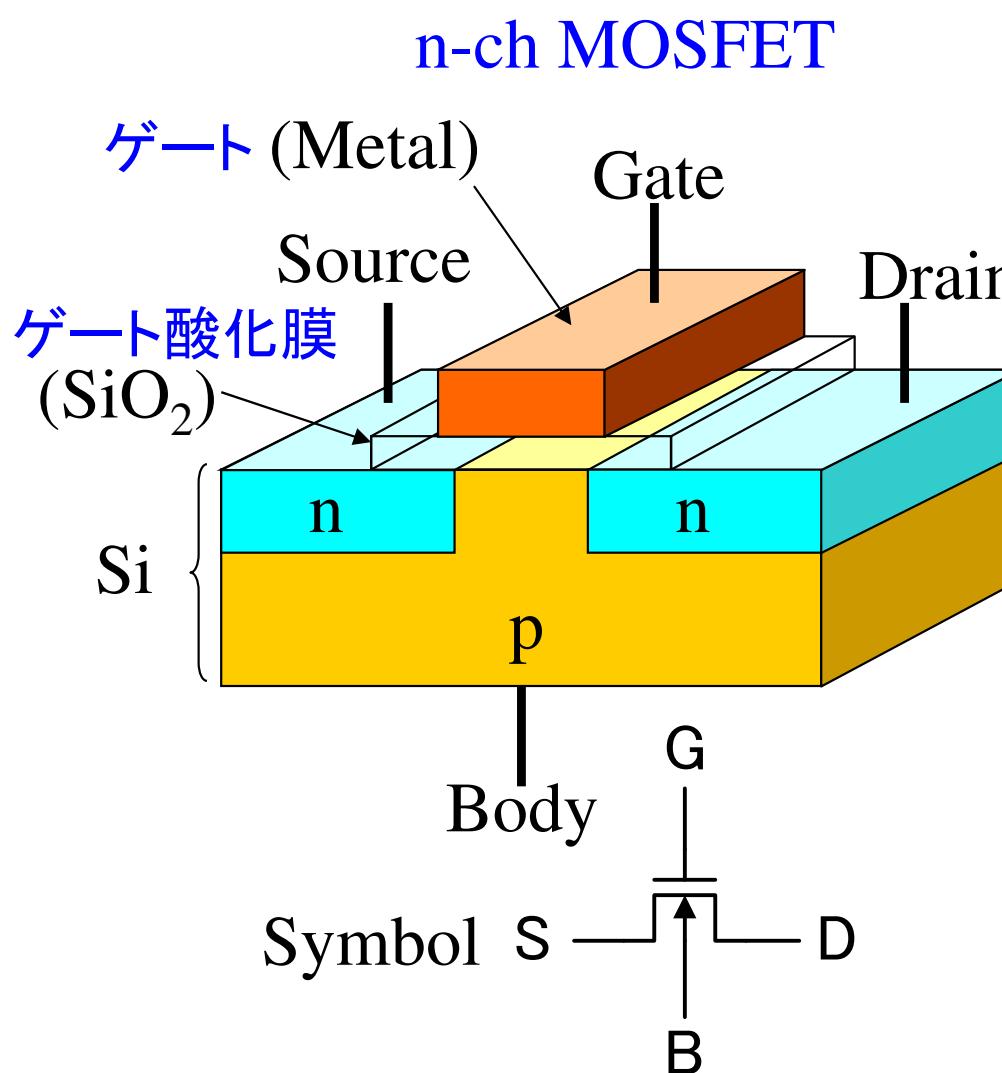

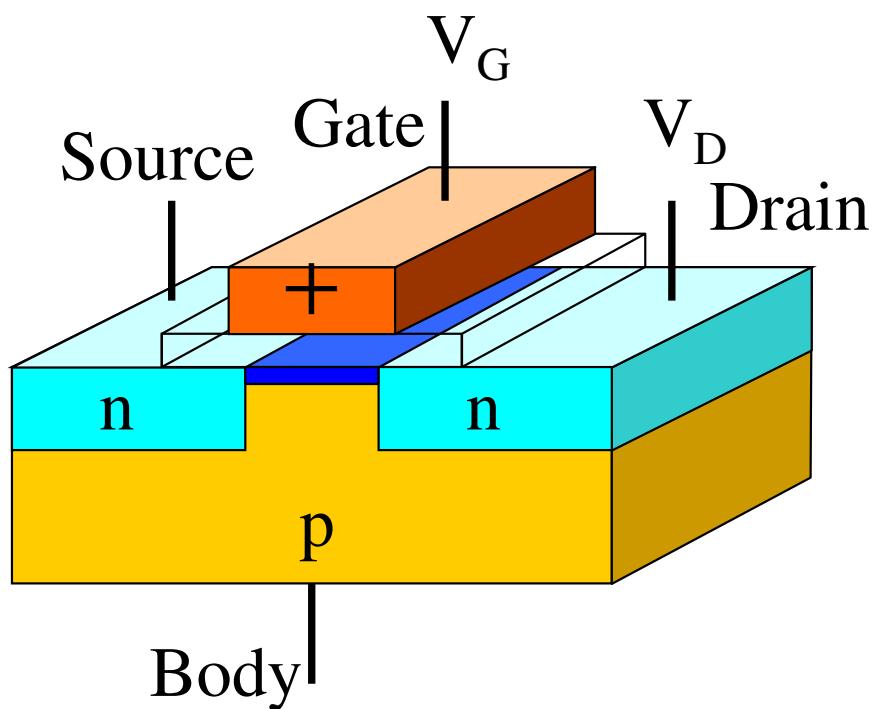

# MOSFETの構造

MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor)

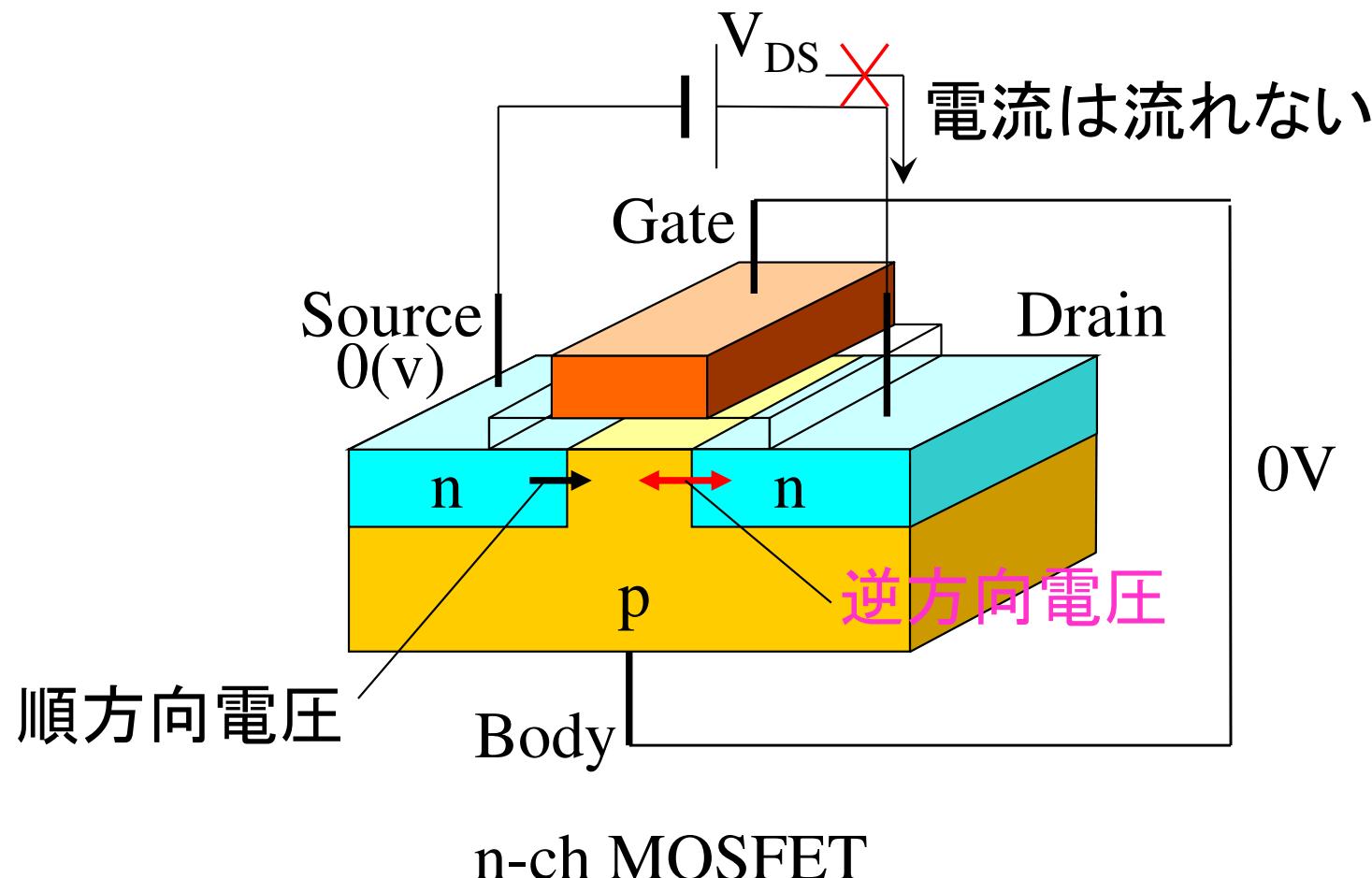

# OFF状態

- チャネルがない状態でソース-ドレインに電圧を加えるとドレンのpn接合が電流を妨げるので、電流が流れない。

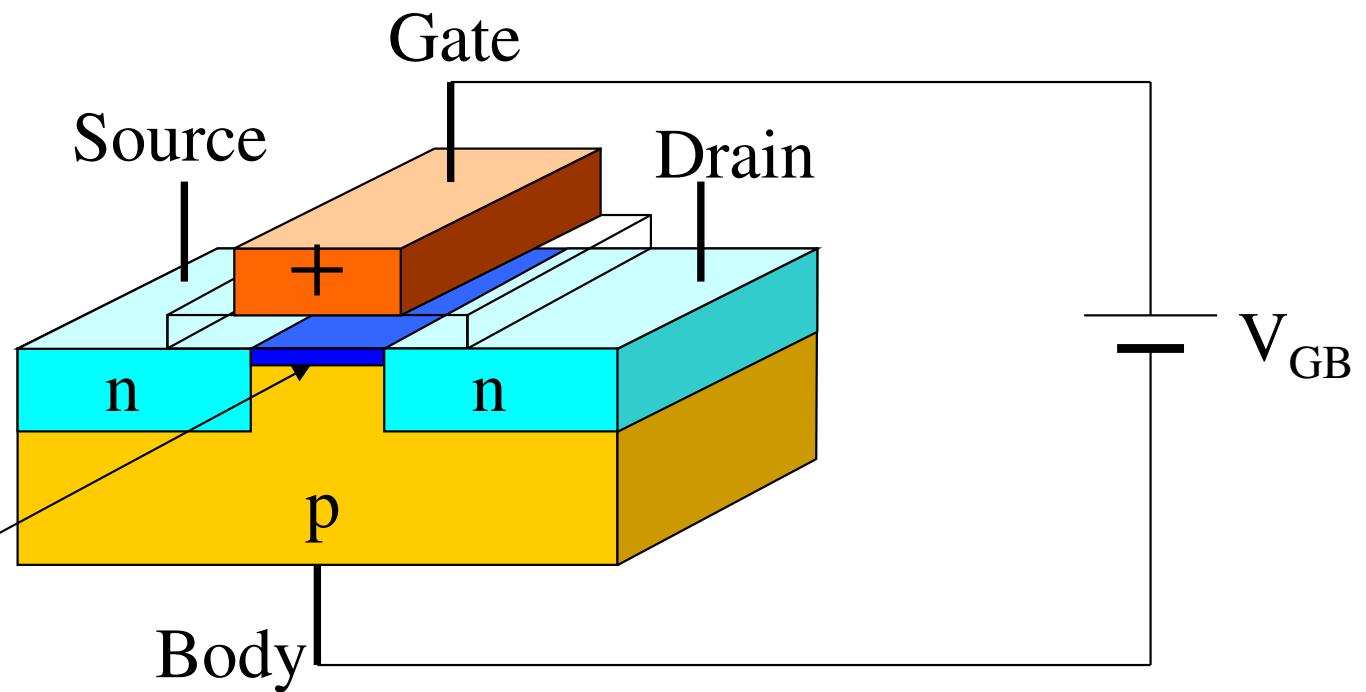

# 電子のチャネル(n-ch)

- ゲート電圧 $V_{GB}$ (正)の印加によりゲートの下の $\text{SiO}_2/\text{Si}$ 界面(MOS界面と呼ぶ)に電子が発生(チャネルと呼ぶ)し、ソース-ドレインの間を導通させる。

電子のチャネルが

発生してn型のよう

に動作する

↑

n-channel

n-ch MOSFET

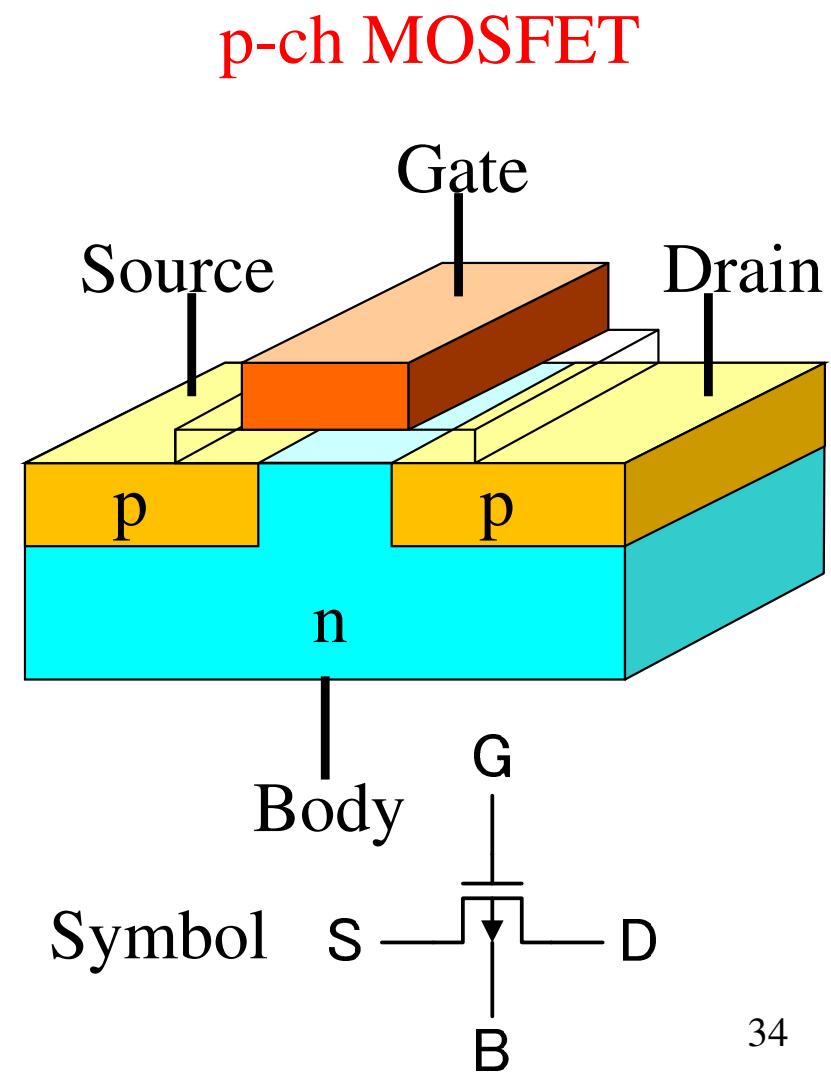

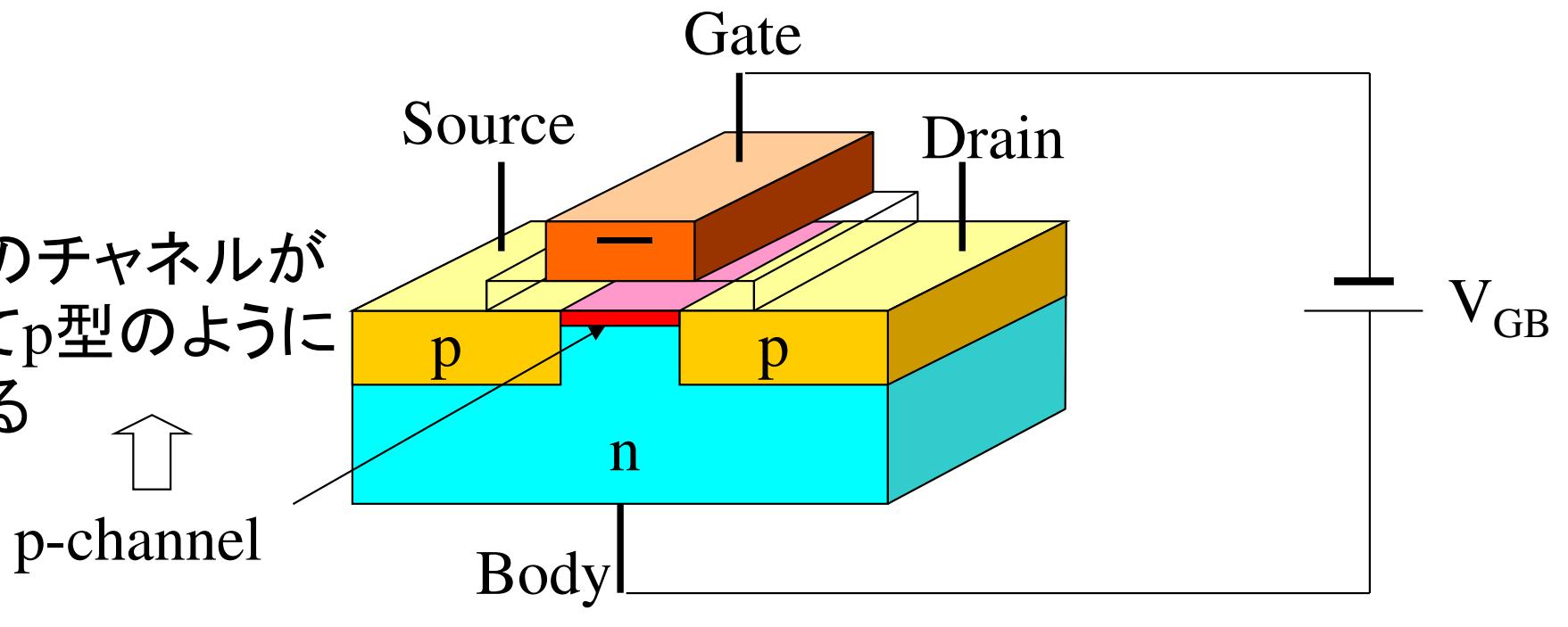

# ホールのチャネル(p-ch)

- ゲート電圧 $V_{GB}$ (負)の印加によりゲートの下の $\text{SiO}_2/\text{Si}$ 界面(MOS界面と呼ぶ)にホールが発生(チャネルと呼ぶ)し、ソース-ドレインの間を導通させる。

ホールのチャネルが

発生してp型のように

動作する

p-ch MOSFET

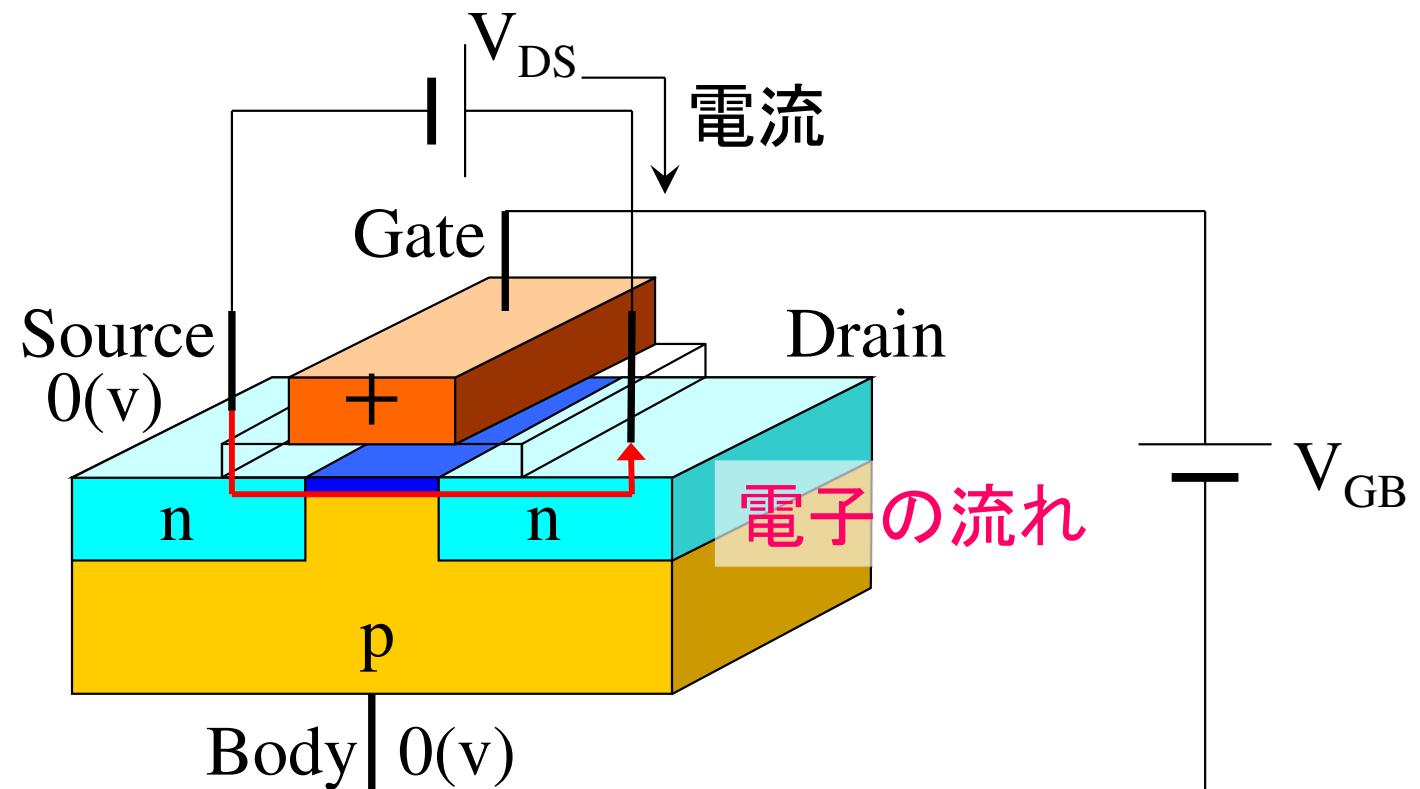

# ON状態(n-ch)

- チャネルが発生した状態でソース-ドレインに電圧を加えると電子による電流が流れる。

n-ch MOSFET

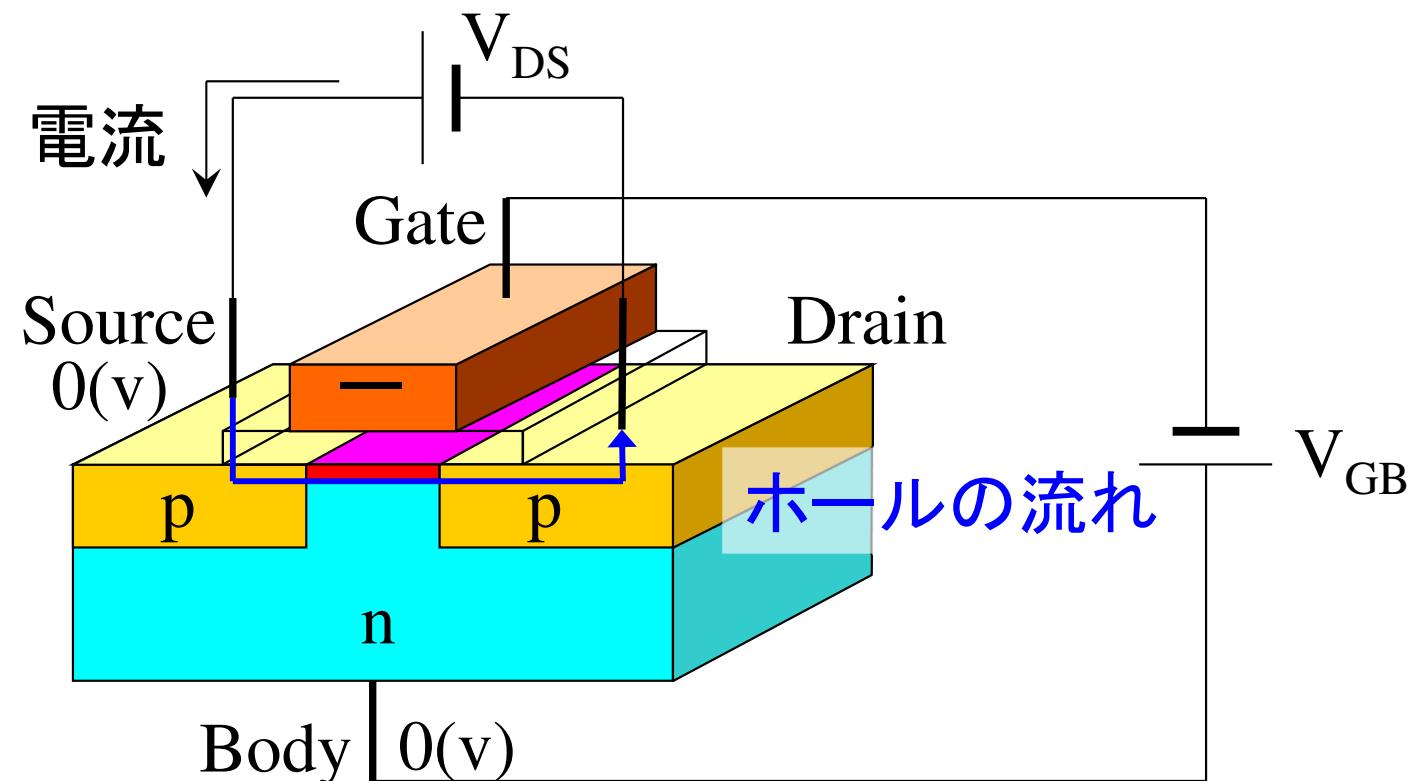

# ON状態(p-ch)

- チャネルが発生した状態でソース-ドレインに電圧を加えるとホールによる電流が流れる。

p-ch MOSFET

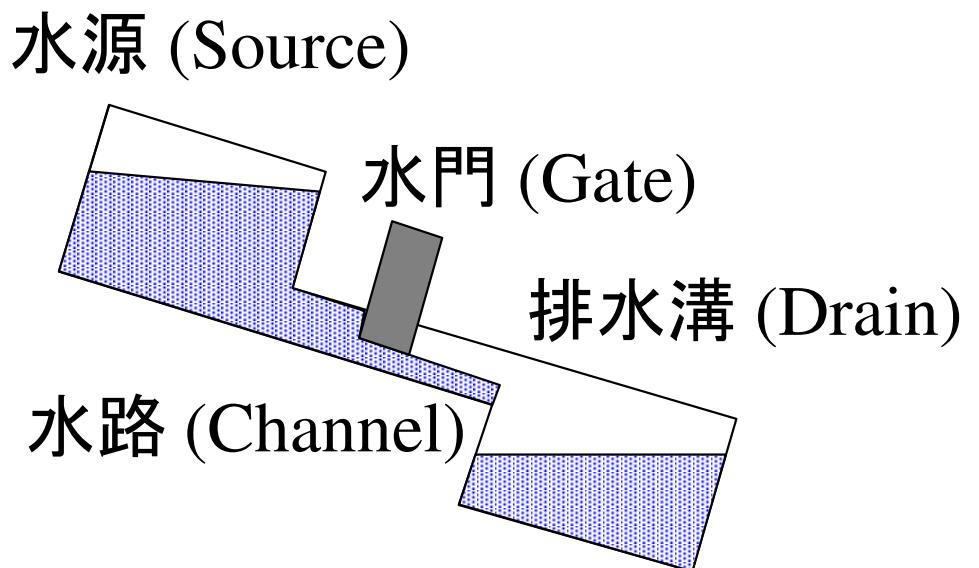

# 電極名の由来

# 9.4節のまとめ

- MOSFETの構造

- MOS(Metal-Oxide-Semiconductor)構造の中に2個のpn接合を持つ構造となっている

- Drain, Gate, Source, Body(または Bulk)の4コのターミナルを持っている

- MOSFETの動作原理

- $V_{GB}$ によりチャネルの電位(=チャネルの発生量)を制御し、 $V_{DS}$ によりドレイン電流 $I_D$ を流す

- n-ch MOSFETとp-ch MOSFETの2種類があり、n-ch MOSFETは、電子のチャネルを発生させ、p-ch MOSFETはホールのチャネルを発生させることによりドレイン電流を流す

- n-ch MOSFETは、 $V_{GB} > 0$ でチャネルが発生し、p-ch MOSFETは、 $V_{GB} < 0$ でチャネルが発生する

- n-ch MOSFETの電子分布

- n型半導体は、電子にとってポテンシャルが低く、電子が溜まっている

- p型半導体は、電子にとってポテンシャルが高く、障壁になっている