- 練習用DUTに搭載したジョンソンカウンターのVerilogHDL記述とテストベンチをコピーして デスクトップの jcnt4 フォルダに、jcnt4.v, tb_jcnt4.v のファイル名で保存

- $dumpfile は出力先のVCDファイル名を指定します。$dumpvars は、出力する変数を指定します。第1引数に'0'を指定すると全階層の変数を出力できます。$dumpflash は、シミュレーション結果をメモリからファイルに書き出します。このテストベンチは、GUIを使用することを想定しています。Verilog-XLなどをバッチモードで実行する場合は、$stop; の代わりに $finish; を使ってください。この場合は、$dumpflash がなくてもかまいません。

ジョンソンカウンタのVerilogHDL記述 (jcnr4.v)

module jcnt4 (CLK, CLR_B, PR_B, Q); input CLK, CLR_B, PR_B; output [3:0] Q; reg [3:0] Q; always @(negedge CLR_B or negedge PR_B or posedge CLK) begin if (!CLR_B) begin Q <= 4'h0; end else if (!PR_B) begin Q <= 4'hf; end else begin Q <= Q << 1; Q[0] <= ~Q[3]; end end endmodule

テストベンチのVerilogHDL記述 (tb_jcnt4.v)`timescale 1ns/1ns module tb_jcnt4; reg r_clr_b, r_pr_b, r_clk; // Clear, Program, Clock wire [3:0] w_q; // Output parameter cycle = 200; // Clock period = 5MHz parameter treset = 100; // Reset period parameter pc = 10; // Finish cycle jcnt4 DUT(.CLK(r_clk), .CLR_B(r_clr_b), .PR_B(r_pr_b), .Q(w_q)); // Reset or Preset initial begin #0 r_clr_b <= 1'b0; r_pr_b <= 1'b1; #(treset) r_clr_b <= 1'b1; #(pc*cycle) $stop; end // Clock initial begin #0 r_clk <= 1'b0; #(cycle/2) forever #(cycle/2) r_clk <= ~r_clk; end // Monitor and value change Dump initial begin // $monitor($time,, "CLR_B = %b PR_B = %b Q = %h CLK = %b ", r_clr_b, r_pr_b, r_clk, w_q); // VCD file name $dumpfile("jcnt4.vcd"); // VCD signal name $dumpvars(0, DUT.CLR_B, DUT.PR_B, DUT.CLK, DUT.Q); // VCD flush #(treset + pc*cycle) $dumpflush; end endmodule - VerilogHDLシミュレーション

- ここでは、無料で配布されているModelsim FPGA Intel Starter Edition を使用して説明しますが、上記のVerilogHDL記述で出力される VCD (Value Change Dump)ファイルを介してパターンを作成しますので、どのシミュレータでも違いはありません(シミュレーションを実行すればVCDファイルが作成されます)。

- Modelsimを起動

- メニューより、[File] - [Change Directory...] を選び、先ほどVerilogHDLファイルを保存しておいた jcnt4 フォルダを指定

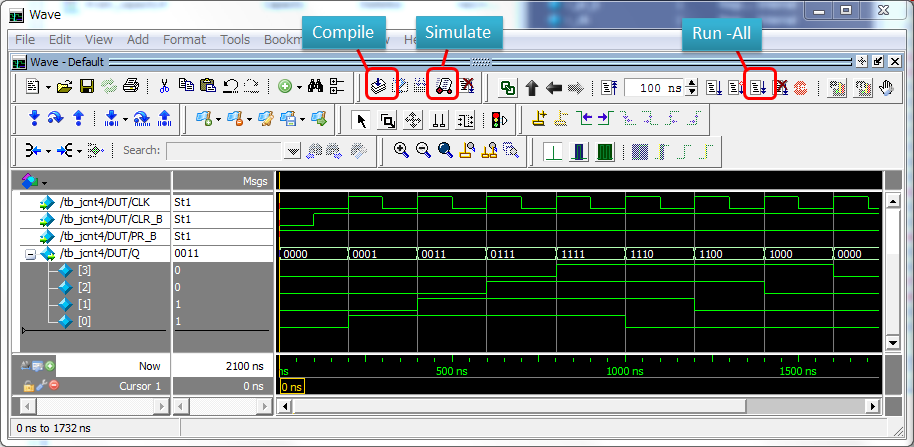

- Compileボタンをクリックし、VerilogHDLファイル(jcnt4.v, tb_jcnt4.v)を選択し、ファイル選択画面のCompileボタンを押す

- Transcriptウインドウに、Erooros: 0, Warnings: 0 と表示されたら、ファイル選択画面のDoneボタンを押す

- Simulateボタンをクリックし、Start Simulation フォームで、[work] - [tb_jcnt4]を選んで、OKボタンをクリック

- m-Default欄(左側窓)で、DUTを選択(シミュレーション対象のインスタンス名)

- Objects欄(右側窓)で、CLK, CLR_B, PR_B, Q を選んで右クリックし、ポップアップメニューで、[Add Wave]を選択すると、信号名に、CLK, CLR_B, PR_B, Q が表示された状態で、波形表示ウインドウが起動する

- 波形ウインドウのツールバーかで、[Run -All]ボタンをクリック

- 正しい波形が表示されていることを確認して、Modelsimを終了

- jcnt4 フォルダ内に jcnt4.vcd が作成されていることを確認

- VCDファイル - NIテキストパターンファイル変換

- Digital Pattern Editorは、VCDファイルを直接読み込めませんので、一旦、NI社のテキストパターンファイル(.digipatsrc)に変換します。各種のテスト言語やダンプリストなどからテキストパターンファイルに変換できるツールがいくつか販売されていますが、高機能なだけに、ライセンス料もそれなりに必要です。そこで、「VCD-NIテキストパターンファイル変換ツール」を自作しました。欲しい人は、本ページの作者までご連絡ください。ただし、Double Data Rate の波形には対応していません。また、Perlをインストールする必要があります。

- デスクトップ\VIフォルダから vcd2ni.pl ファイルを、VerilogHDLシミュレーションを行った jcnt4 フォルダにコピー

- Windows PowerShellを起動

- 下記のコマンドを実行(デスクトップのjcnt4フォルダにVCDファイルをおいた場合を想定)

cd .\Desktop\jcnt4 perl vcd2ni.pl --clock_name=CLK --waveform=RL --pattern_name=verilog_pattern --timing_name=CNT_RUN jcnt4.vcd

- perl vcd2ni.pl -h で、オプションのリストが表示されます。--data_rate オプションは機能していません。

オプションの内容

- --clock_name

- クロックがある場合は、クロック名を指定します。クロック名の信号エッジを検出して1サイクルとして処理します。NONEの場合は、全ての信号変化をサイクルの開始と見なします。

- --waveform

- クロック名で指定した信号の波形を指定します。RLの場合は立ち上がりエッジをサイクルの開始、RHの場合は、立ち下がりエッジをサイクルの開始、NRの場合は、立ち上がりと立ち下がりエッジをサイクルの開始と見なします。SBCは指定できません。

- --pattern_name

- パターンファイルにはパターンネームが付くので、ここで指定します。指定しなければ、デフォルトの名前になります。

- --timing_name

- パターンファイルの作成にはタイミング設定に付けた名前が必要なので、ここで指定した名前を全てのサイクルに適用します。リセットやウエイトなどの特殊な状況でのタイミング設定を使うときは、後でパターンファイルを修正してください。

- VCDと同じファイル名で拡張子.digipatsec のファイル(ここでは、jcnt4.digipatsrc) が jcnt4 フォルダに作成されているはずなので、これをTrainingフォルダ(Digital Pattern Editor のプロジェクトフォルダ)にコピーする

- テキストパターンファイルのインポート

- テキストパターンファイルをPXIe-6570のパターンベクタとして使用するためにコンパイルします。

- Digital Pattern Editor で、Trainingプロジェクトを起動した状態で、メニューより、[File] - [Import Pattern...] を選ぶ

- jcnt4.digipatsrc を選択して、開くボタンをクリック

- 前回インポートしたパスを記憶しているので、正しいパスかどうか注意。

- 保存ファイル名(バイナリパターンファイル .digipat)を聞いてくるので、そのままでよければ、保存ボタンをクリック

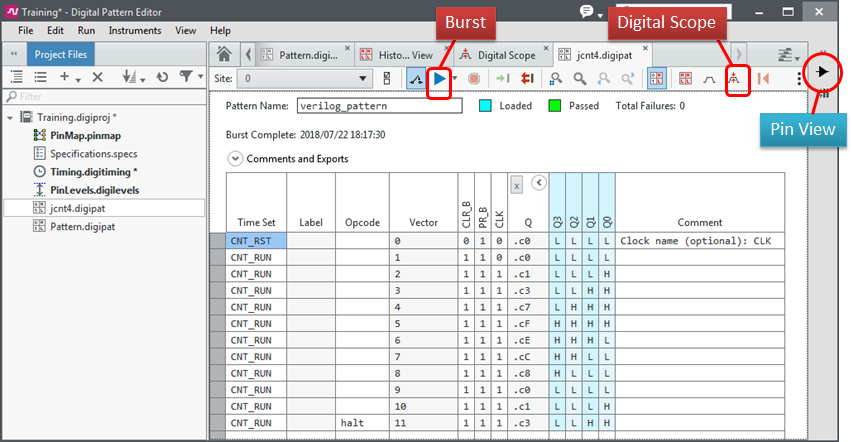

- インポートされたPatternファイルが、プロジェクトに表示されるので、ダブルクリックして内容を確認

- 1行目のタイムセット列をダブルクリックして、CNT_RSTに変更

- リセットのサイクルも定常動作サイクルとして定義したCNT_RUNとなっているので、リセット用に設定したタイミングデータCNT_RSTに差し替えます。また、クロックは、RL波形を指定したため、'10'ではなく'1'で1周期となります(0の場合はクロック停止)。

- 動作確認

- 測定の実行手順は、手動パターンのときと同じです。

- 左のPin Viewボタン(黒三角アイコン)でPin = VDD2を選び、VFスイッチをONにする

- ツールバーのバーストボタン(青い三角)をクリック

- エラーがないことを確認

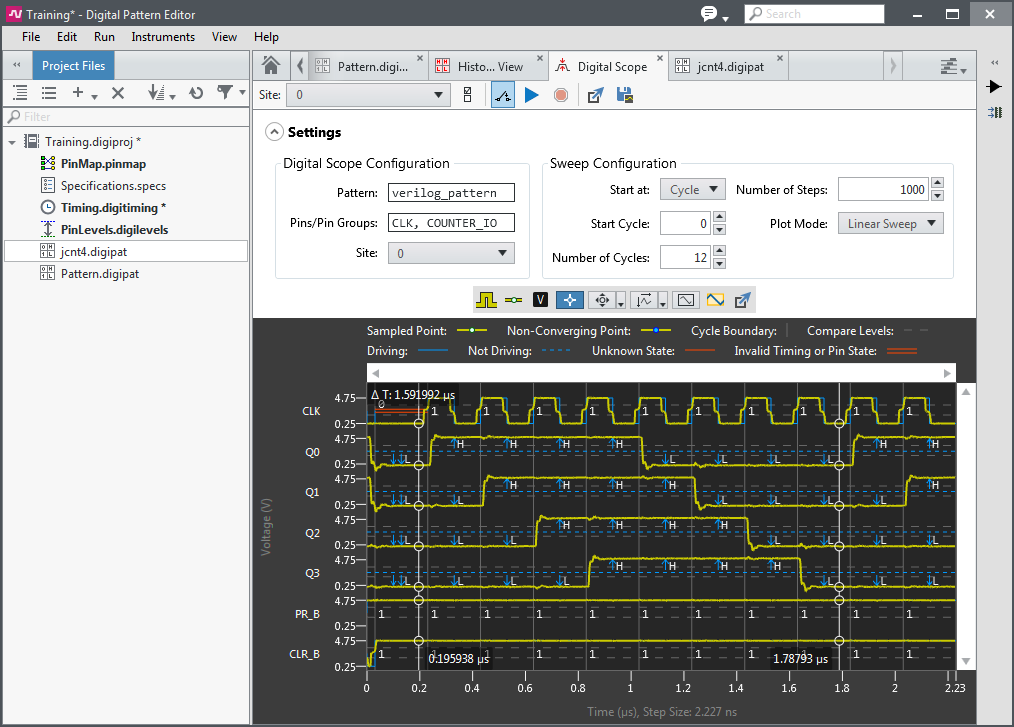

- ツールバーのShow Digital Scopeボタン(波形に赤い矢印がついたアイコン)をクリック

- 下図のDigital Scope Settings欄のように設定を行う

- Pattern = verilog_patternとなっていることを確認してください。デフォルトでは、前に使用したInverterのパターンが設定されています。