ミニマルファブのPDK(Process Design Kit)を使用していて、公開されているマニュアルだけではわからない細々としたヒント、気付いた点をこちらにまとめておきます。

MOSFETのゲート長

ミニマルファブのMOSFET製造プロセスは自己整合プロセス(イオン注入によるソース、ドレイン形成)ではないため、ゲート電極とソース、ドレインのオーバラップが任意に設計できる。オーバラップ長が変わればMOSFETの電気的特性も変わるため、回路シミュレーションとレイアウトを一致させる必要がある。この辺りを、どのように処理しているのか不明だったが、どうやら下記のようになっているらしい。

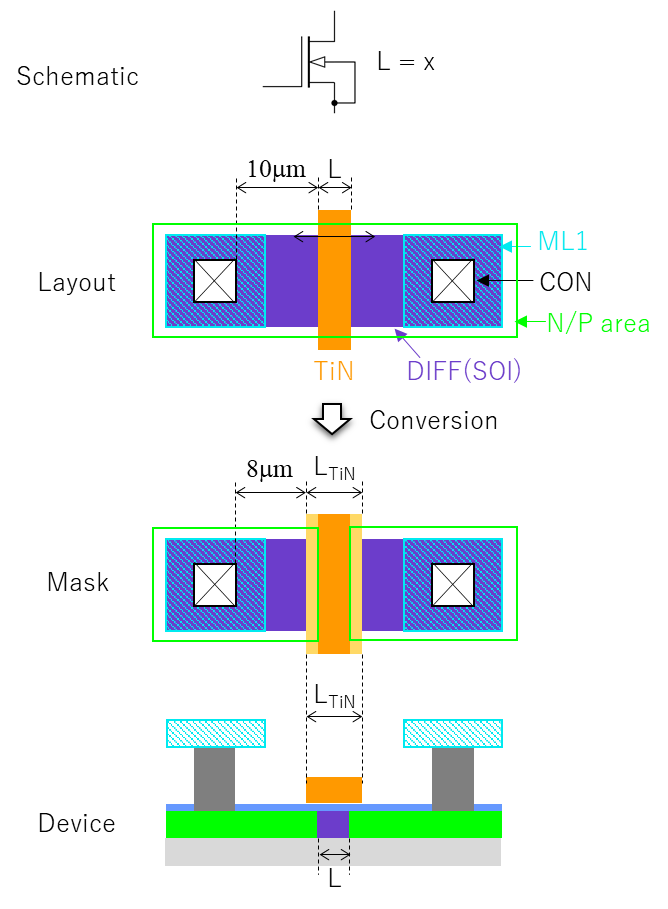

- ゲート長をLTiNで表し、チャネル長(実効ゲート長)をLで表す。回路シミュレーションのゲート長は、チャネル長Lを使用し、同じLの値でレイアウトを行なう。

- TiNゲート電極とコンタクトの間は、10um以上空けておく。

- LVSは、回路図のLとレイアウト図のLを一致させる必要がある。

- KLayoutのメニューより、Macros – ICP2023_5 to SOI conversion を実行。

- 表示レイヤーがマスクレイヤー番号に変換され、”セル名_converted.gds” としてエクスポートされる。

- この処理により、TiNゲートが両側に2um拡張され、LTin = L + 4um となる。また、拡張されたゲート電極の下は、Narea または Pareaとなり、2umのオーバラップが形成される。(下図参照)

- [注意1] TiNゲートとコンタクトの距離は、設計値10umから、変換により8umに縮小される。設計規則では、TiNゲートとコンタクトの距離 \(\geq\) 8umとなっているが、DRCでは、6um(設計値8um)でパスするので、設計値を8umとしてもよいのかもしれない。

- [注意2] ゲート長が拡張されるGate Extension(ゲートフリンジ)の長さは、4umになっているので、Gate Extension = 4um丁度にしてTiN配線に接続すると、DRCエラーが発生しない。

- [参考] 変換前のレイアウトでは、自己整合プロセスと同様、Narea または Pareaは、DIFF(SOI)全体を囲むように描く。レイアウト変換により、チャネル部分から、Narea または Pareaが除外され、マスク整合プロセス用のパターンになる。

- 変換後の”セル名_converted.gds” は、KLayoutのメニューより、Tools – LVS – LVS for ICPS2023_5 product によりLVSを実行し、変換が正常に行われたことを確認できる。

TiN抵抗とキャパシタ

- TiN抵抗

- PDKのマニュアルでは、TiN(ゲート電極材料)のシート抵抗が記載されている。PCellからBridgeというセルを呼び出すと、TiNにRES(抵抗レイヤー)を付したレイアウトに抵抗値が表示される。しかし、この抵抗はLVS(レイアウト回路図等価性検証)では抵抗として認識されず、エラーとなる。LVSをパスするためには、R_ndiff(低抵抗), R_pdiff(高抵抗)を使用。

- TiN-ML1キャパシタ

- 一方、TiN-ML1(メタル1)間キャパシタの容量は、PDKのマニュアルに表記されていないが、SOI CMOSのマニュアルには記載されており、PCellにTIN_capとして登録されている。TIN_capを呼び出すとCAP(キャパシタレイヤー)を付したレイアウトに容量値が表示され、こちらは、LVSでキャパシタとして認識される。

B端子のあるMOSFETのDRCとLVS

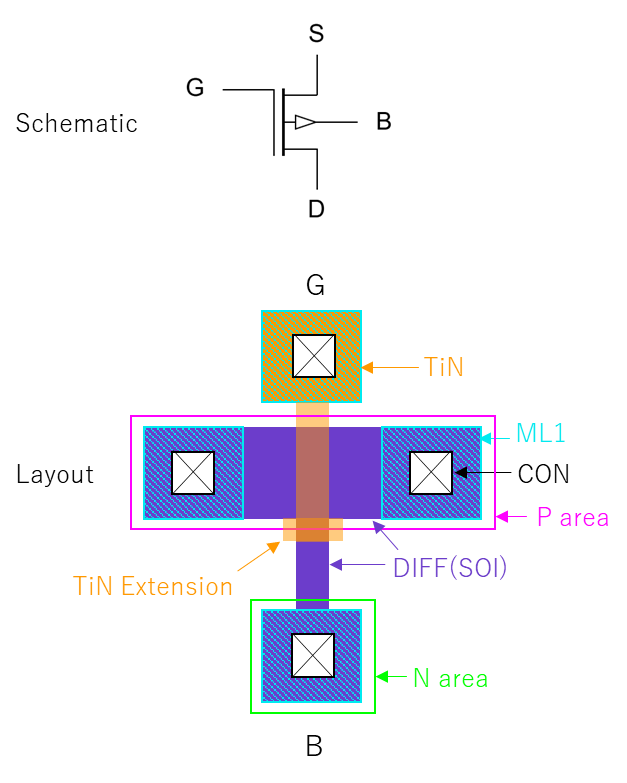

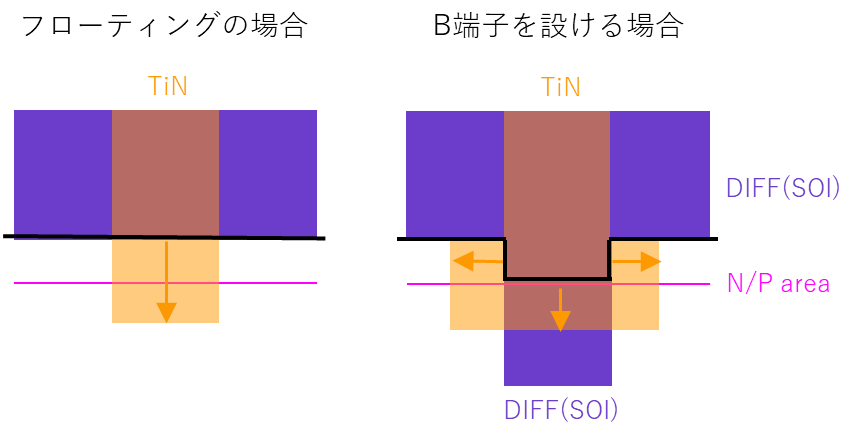

ミニマルファブのトランジスタは、完全空乏型SOI MOSFETであり、通常は、B端子(ボディ)を設けず、ボディをフローティング状態で使用して問題ないと思われる。しかし、閾値変動抑制、放射線対策、DTMOS構造、リーク電流制御等のためB端子を使いたい場合もある。B端子付きのMOSFETを、DRC(設計規則検証)とLVS(レイアウト回路図等価性検証)に通す方法についてまとめておく。

- B端子のレイアウト

- 下図にB端子付きp-ch MOSFETのレイアウト例を示す。TiN Extensionについては、2項以下を参照。

- DRCの実行

- DIFF(SOI)をチャネルから引き出したため、チャネルドープされたエリア(チャネル領域)が凸型になる。このため、Gate Extensionの設計ルールが横方向にも適用される。

- チャネル領域に凹凸がある場合のゲートの設計ルールは、チャネル領域が直線の場合(Gate Extension \( \small \ge 4\mu \mathrm m \))と異なるようで、Gate Extension \( \small \ge 2\mu \mathrm m \) で十分。

- LVSの実行

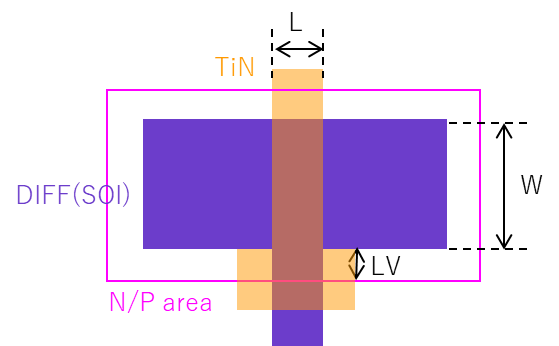

- チャネル領域に凹凸がある場合は、通常のゲート長\( \small L \)に加えて、凸部のゲート長\( \small LV \)が、レイアウトから抽出するゲート長\( \small LE \)に算入されるらしい(下図参照)。\( \small LE \)は、以下の式により求められる。\[ \small LE = L \biggl(1 + \frac{LV}{W} \biggl) \]

- 回路図のゲート長\( \small L \)の値を\( \small LE \)の値に変更してからLVSを実行する。LVSにパスするためには、7桁以上の精度でゲート長を設定する必要がある。

- [注意] ミニマルファブのネットリスト抽出では、B端子を無視しているようなので、B端子の配線にミスが無いよう注意が必要。