ミニマルファブから無料公開されているSOI CMOSプロセスPDK(Process Design Kit)を使用してみます。ただし、私はミニマルファブでチップを試作したことがないので、実際にこの設計手順で製造が可能かは分かりません。産総研インダストリアルCPS研究センターでチップ試作が可能なようですので(ただしメタルは1層のみ)、近日試したいと思います。

開発環境のインストールは、こちらの投稿を参考にしてください。

- 参考資料

- PDK User Manual

- ~/.klayout/salt/ICPS2023_5/Technology/doc/ 配下のPDK_minimalFabSOICMOS.pdfとPDK_reference_manual.pdf

- (株)アナジックス ミニマルファブシャトル

1.回路図作成

回路図エディタは、EEschema(KiCAD), LTspice, Xschemに対応しているようです。ここでは、操作が簡単なXschemを使用します。

以降、作業ディレクトリを /home/ユーザ名/work として説明します。WSLのUbuntu端末から、Xschemをフォアグラウンドで起動してください。

cd ~

mkdir work

cd work

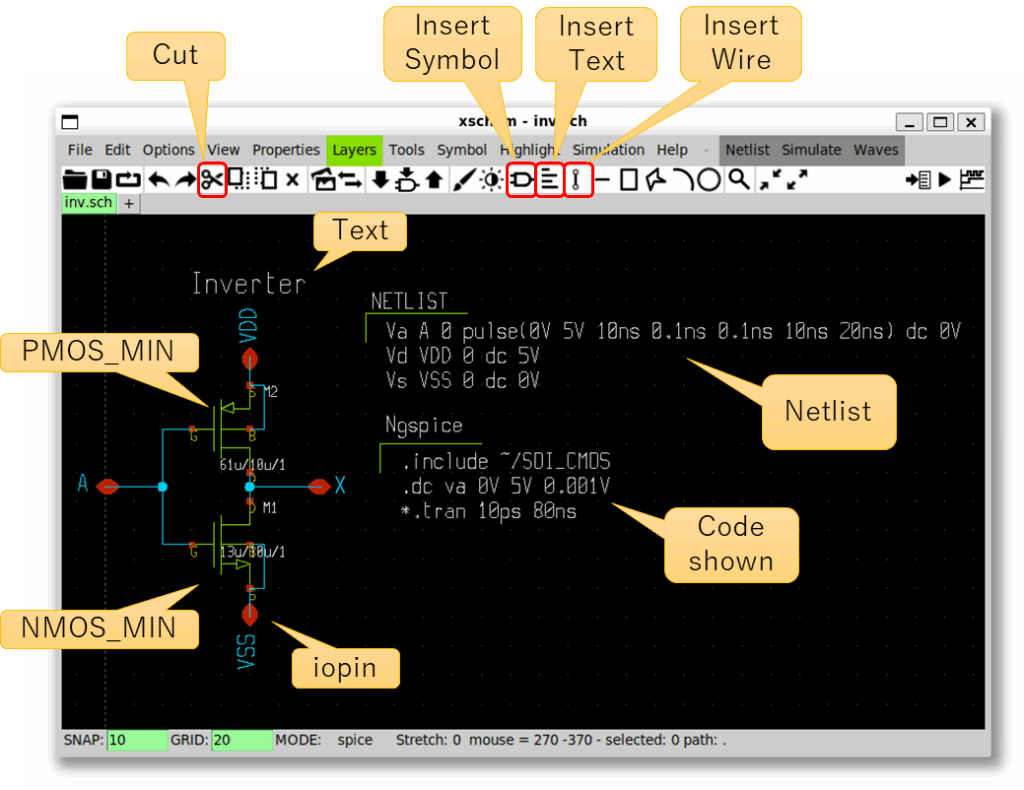

xschemもし、起動画面になにかの回路が表示されているようなら、メニューより、File – Create new window/tab を選んで新しい入力シートを表示させてください。ここに下記のようにインバータの回路を入力します。

- 回路名や回路の説明は、ツールバーの”Insert Text”ボタンまたは tキー で入力します(入力しなくても問題はないが、何の回路で誰が何時作ったのか分かると便利)。

- 回路部品、入出力ピン、回路シミュレータへの指示等は、ツールバーの”Insert Symbol”ボタンまたは Shift + i で入力します。

- Choose symbolフォームが表示されるので、左欄でシンボルライブラリを選択。ここでは、.klayout/salt/ICPS2023_05/tech/symbols/xschem を使用します。

- 下記表1に従って、部品シンボルと回路シミュレータへの指示欄を呼び出します。シンボル等を選んで、OKボタンを押し、シンボルを配置する場所をクリック。

- シンボルの削除は、シンボルを選択してDELキーまたはツールバーでハサミのアイコンをクリック。

- 配線は、ツールバーの”Insert Wire”ボタンまたは wキー で入力します。ミニマルファブのMOSFETは完全空乏型SOI MOSFET(3端子デバイス)と説明されていますが、Bulk MOFETモデル(BSIM3v3)を流用しているため、4端子のシンボルになっています。B端子はVSSまたはVDDではなく各MOSFETのS(ソース)に接続して使用します(説明書には書いてないのですが、たぶんこれでよいと思います)。

- 回路シミュレータへの命令(SPICE directive)や回路の接続情報(Netlist)もツールバーの”Insert Symbol”ボタンをクリックして入力します。

| シンボル名 | 説明 |

|---|---|

| PMOS_MIN.sym | p-ch MOSFET |

| NMOS_MIN.sym | n-ch MOSFET |

| iopin.sym | ioピン [注1] |

| netlist.sum | Netlist等の入力/表示欄 |

| code_shown.sym | SPICE directive等の入力/表示欄 |

[注1] ipin(入力ピン)、 opin(出力ピン)も用意されているが、SPICE(回路シミュレータ)は、入力、出力、電源の見分けがないため、全てのピンにiopin(入出力ピン)を使用すること。opinまたはipinを使用するとERC(Electrical Rule Check)エラーの原因になることがあります。

- プロパティの設定

各シンボルのプロパティを設定します。シンボルをダブルクリックするか、シンボルを選んで qキーを押して、Edit Propertiesフォームを開き、ピン名や部品のパラメータを設定します。各パラメータは、下記表2のようにしてください。

| シンボル名 | 設定内容 |

|---|---|

| PMOS_MIN.sym | name=M2 model=pch w=61u l=10u m=1 |

| NMOS_MIN.sym [注2] | name=M1 model=nch w=13u l=10u m=1 |

| iopin.sym (A) | name=p1 lab=A |

| iopin.sym (X) | name=p2 lab=X |

| iopin.sym (VDD) | name=p3 lab=VDD |

| iopin.sym (VSS) | name=p4 lab=VSS |

| netlist.sym [注3, 4] | name=s0 value= “Va A 0 pulse(0V 5V 10ns 0.1ns 0.1ns 10ns 20ns) dc 0V Vd VDD 0 dc 5V Vs VSS 0 dc 0V” |

| code_shown.sym [注5] | name=Ngspice only_toplevel=false value= “.include ~/SOI_CMOS .dc va 0V 5V 0.001V *.tran 10ps 80ns” |

[注2] PDKのリファレンスマニュアルには、LTiN (ゲート長)とL (チャネル長)が定義されていますが、回路図(デバイスモデル)では、L (チャネル長)の値を設定します。設計規則より、Lmin = 6um (LTiN = 10um), Wmin = 13umであることに注意。

[注3] 電圧源(直流電源と入力信号源)は、設計する回路に含まれないので、回路図には描かず、netlist.sym の方に記入します。value= の記述内容に改行を入れる場合は、” “で囲むことに注意。

[注4] 集積回路の設計では、GND(ノード番号0)とVSS(電源のマイナス側)を分けることを推奨します。GNDは、グローバルな配線であるため、GNDを含む回路モジュールは、モジュール間で意図しないショートが発生し、部品として使いまわす場合に不都合です。このため、GNDとVSSを同電位で動作させたいときは、0Vの電圧源VsをGNDとVSSに挟んで、GNDとVSSを分けるようにします。

[注5] 回路シミュレータへの命令は code_shown.sym に記入してください。ただし、.control ~ .endc ブロックは使用しないでください。.controlを使用すると、シミュレータの起動オプションがキャンセルされます。

- 回路図が完成したら、メニューより、File – Save as で、回路図を保存してください。(ファイル名:inv.sch)

2.回路シミュレーション

回路シミュレーションは、XschemからNgspiceをバッチモードで呼び出して実行します。

- モデルパラメータファイルのパスを、.include ~/SOI_CMOS と指定したので、ホームディレクトリからPDK内のSOI_CMOSにシンボリックリンクを作成しておきます。

ln -s ~/.klayout/salt/ICPS2023_5/Technology/tech/models/SOI_CMOS ~/SOI_CMOS- Xschem のメニューより、Simulation – Configure simulators and tools を選び、Ngspice batch のラジオボタンを選択し、Accept, Save and Closeボタンをクリックします。これにより、回路シミュレータ(Ngspice)をバッチモードで呼び出します。

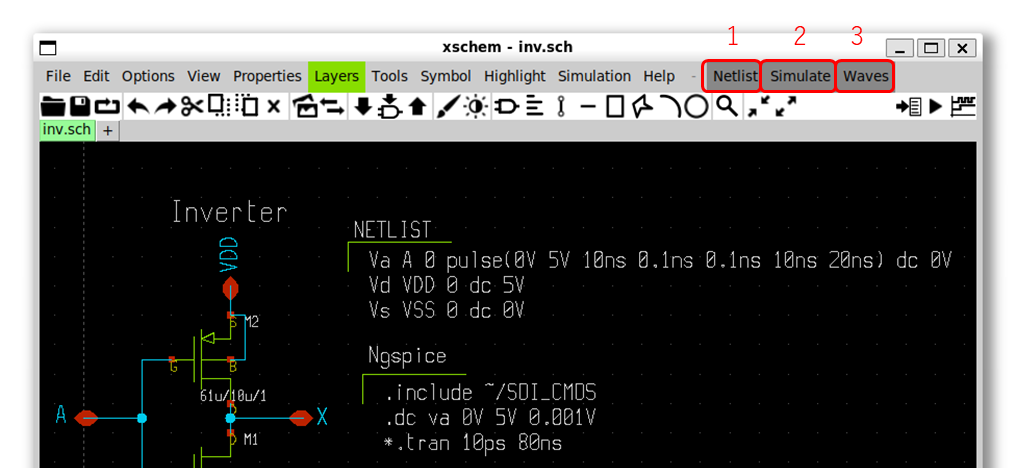

- Xsxhemのメニューバーより、Netlist -> Simulate のボタンを順にクリックします。ボタンが緑色になったら成功です。

- Ngspiceからエラーメッセージが出なければ、メニューバーのWavesボタンより、External Viewerを選択します。Gawの波形ウインドウと信号選択ウインドウが表示されます。

- Gawを使いやすくするため、Gawのメニューより次の設定をしておきます。

- Preferences – show more Y labelsにチェック

- Preferences – Show Gridにチェック

- Preferences – Allow Resizeにチェック

- Preferences – Algorithm List – per-pixelmodified にチェック

- File – Save confを実行(設定の保存)

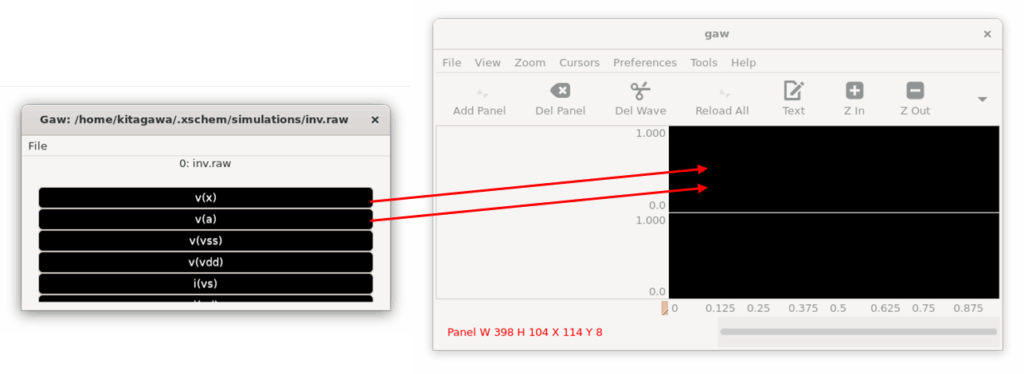

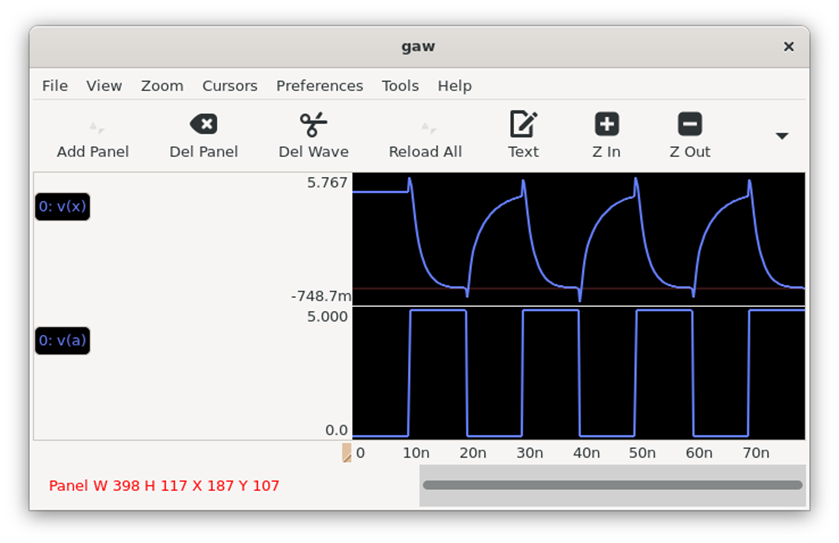

- 信号選択ウインドウから、入力電圧v(a)と出力電圧v(x)を空のグラフ上にドラッグ&ドロップして、波形を表示してください。

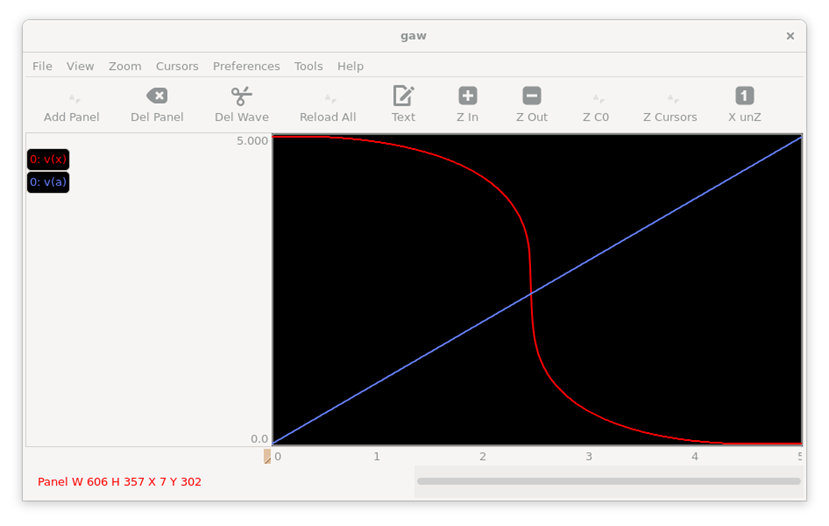

- 不要なグラフは、グラフの上で右クリック – Remove this Panel で消すことができます。グラフウインドウを広げて下図(上)のように表示させてください。横軸が入力端子の電圧、横軸が出力端子の電圧、青線が入力電圧、赤線が出力電圧です。スイッチング閾値がほぼ VDD/2 になります。

- Xschemのcode_show.symの内容を下記のように変更して、シミュレーションを再度実行してみてください。

*.dc va 0V 5V 0.001V

.tran 10ps 80ns"今度は横軸が時間、縦軸が電圧です。下のグラフが入力波形、上のグラフが出力波形です。やや立ち上がりが遅い(つまりp-ch MOSFETの電流値が小さい)ようですが許容範囲です。

3.レイアウト作成

レイアウト設計は、ミニマルPDKが対応しているKLayoutを使用します。下記のように起動してください。-e オプションをつけると、編集モードでの起動になります。

cd ~/work

klayout -e &- メニューより、File – Setup を選び、Setup画面で、表3のように初期設定を行います。この設定は、初回のみです。

| 項目(左欄) | 設定 | 備考 |

|---|---|---|

| Application – Editing Mode | Use editing mode by defaultに☑ | 次回起動から -e オプション不要 |

| Application – Grid | 0.5 | |

| Application – Default Grids | 1,0.5, を追加 | メニュー: View – Grid で 1um. 0.5umを選択できるようにするため |

| Display – Texts | Text font = Stick Standard text size = 10(20でもよいかも) | フォントをdefault以外にしないと、sizeが反映されないので注意 |

| Display – Background | Back ground color を設定 | 見やすい背景色にする(黒など) |

| Rules And Anotations – Snapping | Snap to gridに☑ |

- メニューより、File – New Layout を選択して、レイアウト画面を表示させます。Technology は、ICPS2023_5を選択、Initial window size = 200um(適当で)にしてOKボタンをクリック。

- メニューより、Edit – Editor Options を選択すると、ウインドウ左下にEditor Optionsペインが表示されるので、Basic Editingタブで、表4のように設定します1。この設定は初回のみです。

| 項目(左欄) | 設定 | 備考 |

|---|---|---|

| Angle Constraints – Connections | Manhattan | 縦横方向のみ接続可能 |

| Angle Constraints – Movements | Manhattan | 縦横方向のみ移動可能 |

| Hierarchical Features – Shallow select | Select top level objects onlyに☑ | 下の階層の構造は選択対象から外す |

- 描画モード(PCellの呼び出し後、Boxの描画ボタンクリック後など)でないと、この設定はできません。 ↩︎

- レイアウトの作成の前に、下記の画面操作を覚えておいてください。

- 拡大縮小:マウスホイール

- 左右移動:CTRL + マウスホイール

- 上下移動:SHIFT + マウスホイール

- 画面パン:マウス中ボタンを押してドラッグ

- 全画面フィット:F2キー

[参考] メニューより、File – Setup -> Application – Customize Menu の設定画面で、キーバインドを設定することができます。頻繁に使用する編集モードを設定しておくと、作業効率が飛躍的に向上します。

設定例

- Ruler -> k (ルーラの解除はデフォルトで CTRL + k に設定されている)

- Path -> w (Wire)

- Partial -> s (Stretch)

- Move ->m (Move)

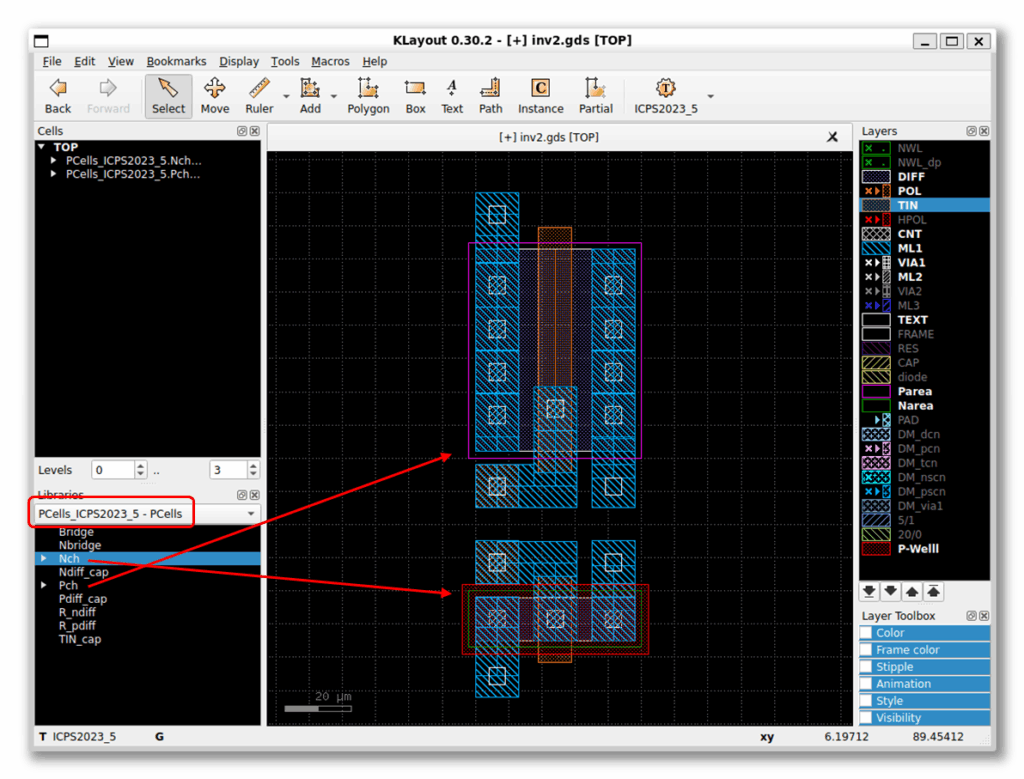

- MOSFETのPCELL (Parametric Cell) を呼び出します。

- 左側のLibraries欄で、Pcells – ICPS2023_5 – Pcells を選択。->[参考]

- Libraries窓に、各種Pcellが表示されます。

- PchとNchのPcellをレイアウトウインドウにドラッグして置きます。

- メニューより、Display – Full Hierarchy を選択すると、Pcell内部の構造が表示されます(編集中の階層より下の階層が表示された)。

[参考] ~/.klayout/libraries を作成して、その中にGDSファイルを置くとKLayoutのLibraries欄にGDSファイルが表示され、編集中のセル(レイアウト部品)として呼び出せます。

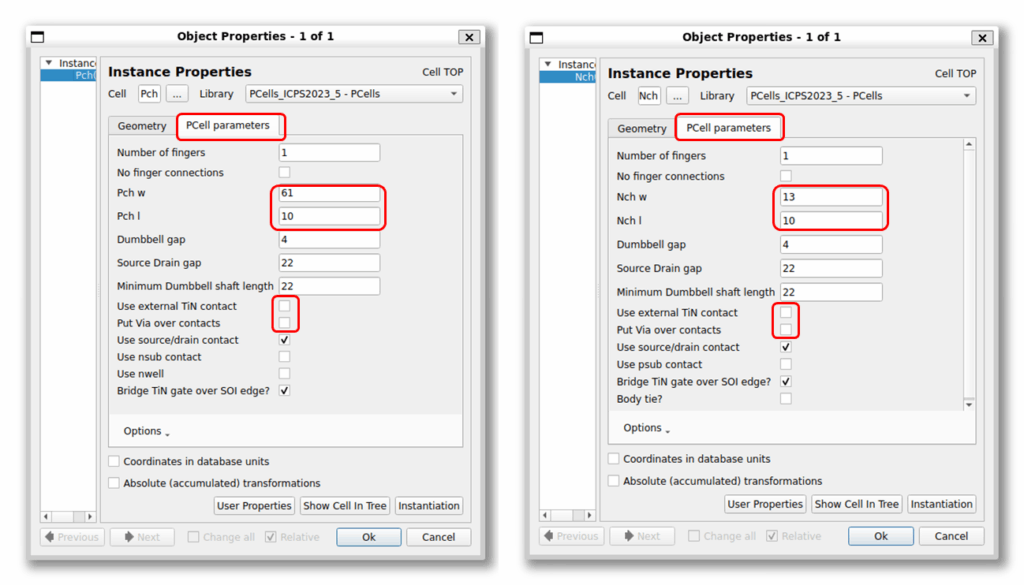

- PCELLのパラメータを設定します。

- n-ch MOSFETのPCELLレイアウトを選択し、qキー(または、メニューより、Edit – Properties)でObject Propertiesフォームを表示させます。

- PCell Parametersタブを開き、回路図と一致するように、Mumber of fingers, Nch w, Nch l等を設定します。チェックボックスは、変更するとレイアウトがどう変化するかを確認し、好みで設定します。PDKの説明ではVIAをなるべく使わないようにとのことなので、Put Via over contact のチェックを外します。とりあえず、下図のように設定してください。

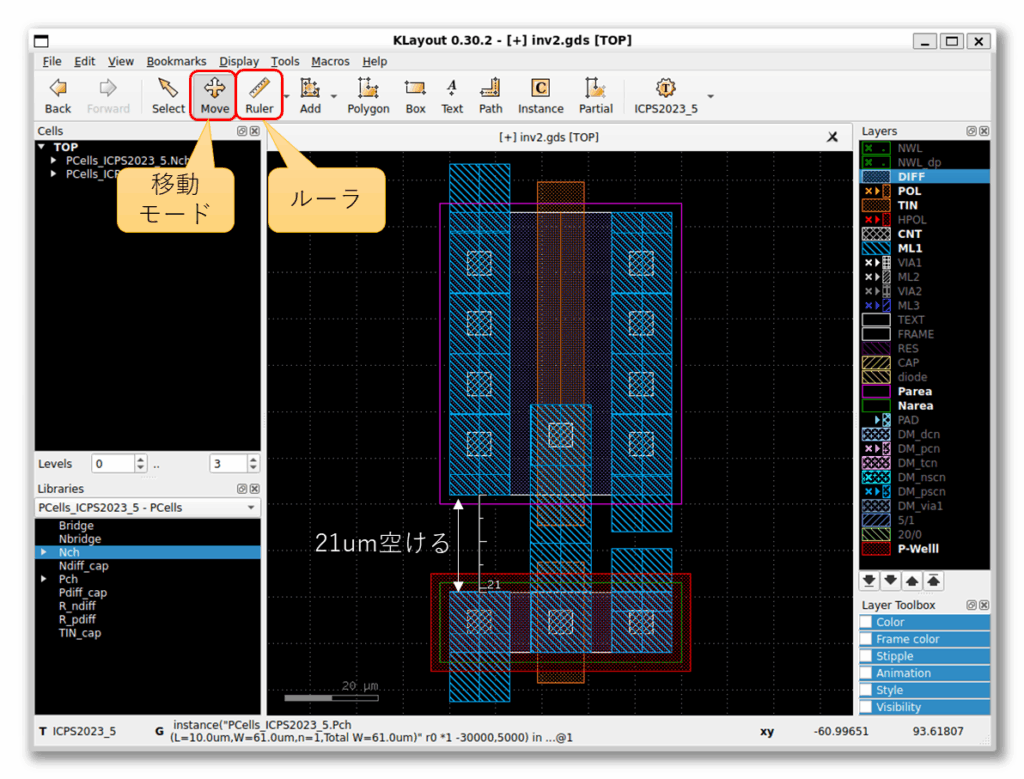

- n-ch MOSFETとp-ch MOSFETの距離を調整します。

- 最小面積でレイアウトができるように下図のように、21umの距離を空けます。なぜ21umにしたのかは、後で解ります。

- 距離は、ルーラで測定します。Rulerボタンをクリックし、レイアウト上をクリックスすると、クリックした点からの距離が表示されます。単位はマイクロメートルです。21umの位置で再度クリックしてルーラを固定します。ルーラモードは、ESCキーで解除します。ルーラモードを抜けても、ルーラは残ります。CTRL + kキーで、ルーラが全て消えます。

- Moveボタンをクリックしてから、PCELLをクリックして移動させます。移動モードは、ESCキーで解除します。

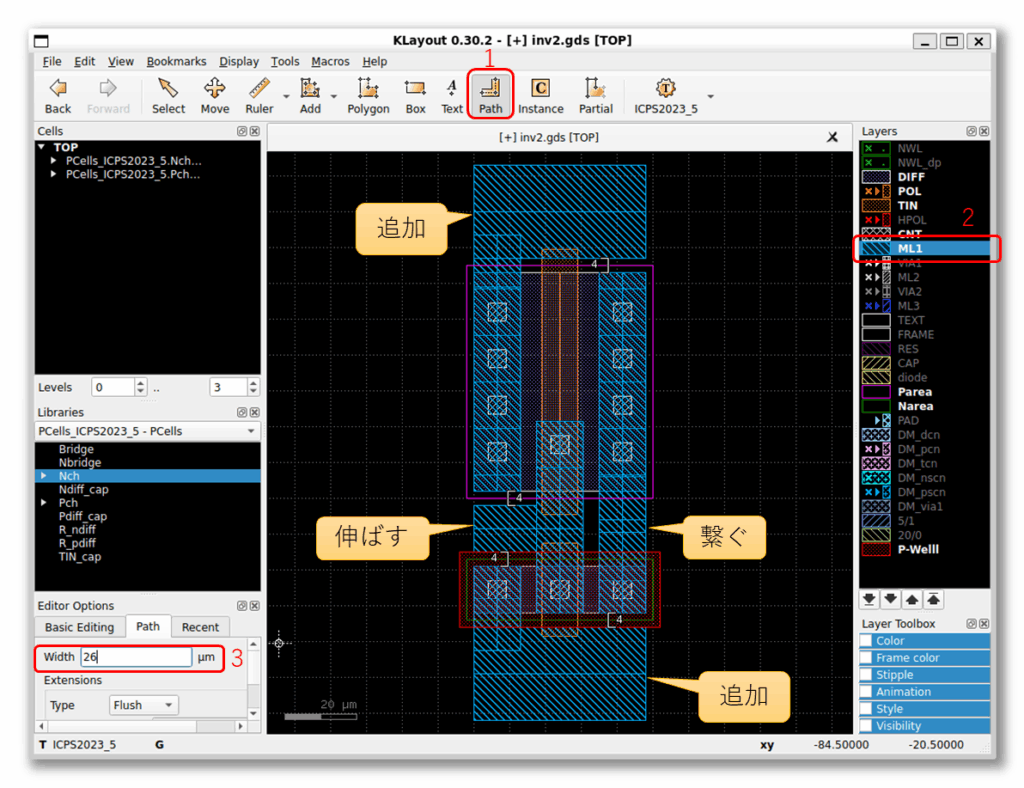

- 配線を行います。配線は、BoxまたはPathで作成することができます。Pathは折れ曲がりができるので、通常はPathが使いやすいと思います。

- 設計規則により、メタル配線間の最小距離は4umなので、配線が近づきそうな場所に、4umのルーラを設置します(下図参照)。

- Pathボタンをクリックし、レイヤー欄からML1(金属層)を選びます。

- 右下ペインにEditor Options欄が現れるので、PCELLの配線幅に合わせて、Width = 13に設定します。

- レイアウト画面上で、クリックすると配線が始まり、ダブルクリックで終了します。ダブルクリックではなくクリックすると折れ曲がりになります。Pathの作成には、少し慣れが必要だと思います。

- 電源配線VDD, VSSは、後で他の回路と繋いだときに抵抗が小さくなるよう(本来は電源ラインに抵抗があってはいけない)、太めにしてみましょう。ここでは、Width = 26 にします。

- 配線Pathは適当に作成しておき、後でMoveボタンにより移動させるという方法もあります。

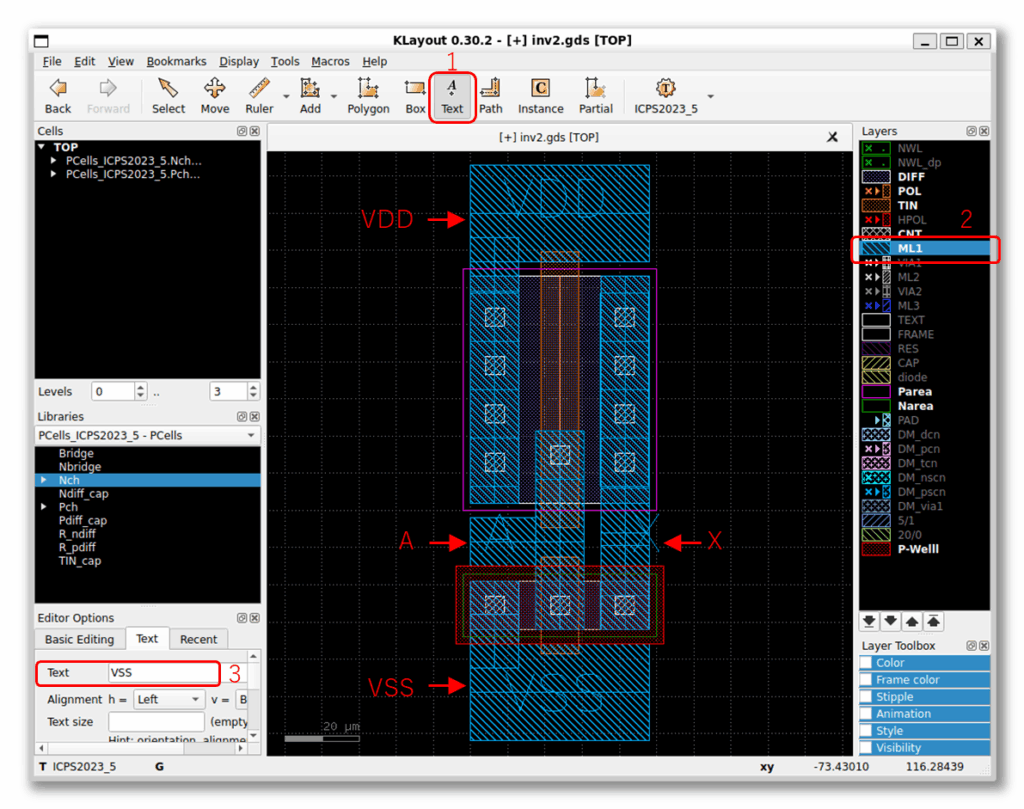

- レイアウト上の配線にPin名を設定します。回路図との対応を取るため、Pin名に対応する配線がどれかを明示しておきます。

- Textボタンをクリックし、名前をつけたい配線のレイヤーを選択します。ここでは、配線にML1を使用しているので、配線名のレイヤーもML1です。

- 右下ペインEditor OptionsのText欄にピン名を入力します。

- レイアウト上をマウスで左クリックすると、その位置にピン名が設置されます。ピン名左下あたりにある+マークが、対象の配線上に乗っていることが必要です。

- レイアウト図が完成したら、メニューより、File – Save As で、レイアウト図をGDSフォーマットで保存してください。(ファイル名:inv.gds)

- 次回、読み込むときには、下記の手順で読み込みます。

- メニューより、File – Open で、読み込むGDSファイルを選択。

- メニューより、File – Load Layer Properties で下記のテクノロジファイルを開く。

~/.klayout/salt/ICPS2023_5/Technology/tech/ICPS2023_5.lyp- 毎度、テクノロジーファイルを開くのが面倒な場合は、下記の設定を行います。

- メニューより、File – Setup で、Setup画面を表示

- Application – Layer Properties を選択

- Use default layer properties にチェック

- ファイル指定のボックスに、上記のテクノロジファイルのパスを入力してOKボタンをクリック

以上でインバータのレイアウトは完成ですが、PDKマニュアルには示されていないレイヤー名が表示されていて、?なところもあります。レイヤ番号と照合すると下記のように読み替えできそうです。また、PCELL内部が自己整合プロセスを想定したレイアウトになっていますが、後でフォトマスクアライメント形式に自動変換されているようです。恐らく、他のミニマルファブプロセスとテクノロジデータを共有しているためではないかと思われます。

| Layer表示 | 実際のLayer |

|---|---|

| DIFF | SOI |

| TIN | TiN-Gate |

| CON | Contact |

| ML1 | M1 |

| Parea | P-diff |

| Narea | N-diff |

| P-Well | N-ch |

4.DRC (Design Rule Check)

手動でレイアウトを行った場合は、DRCが必須です。DRCをパスしていないデータでは製造ができません。

- KLayoutのメニューより、Tools – DRC – DRC for ICPS2023_5 を選択。

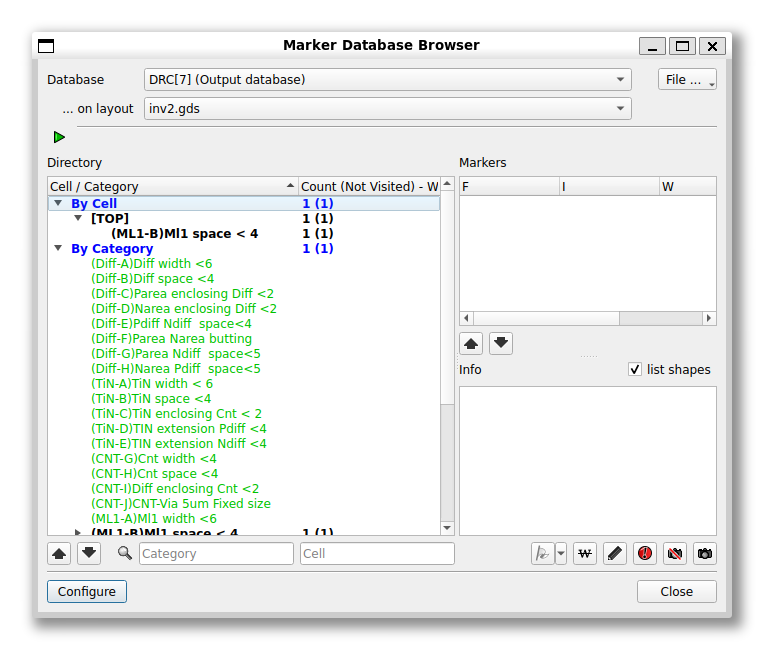

- DRCが実行され、Marker Databese Browserが表示されます。

- Directory欄(左側)の全てのチェック項目が緑になっていれば、DRCをパスしています。

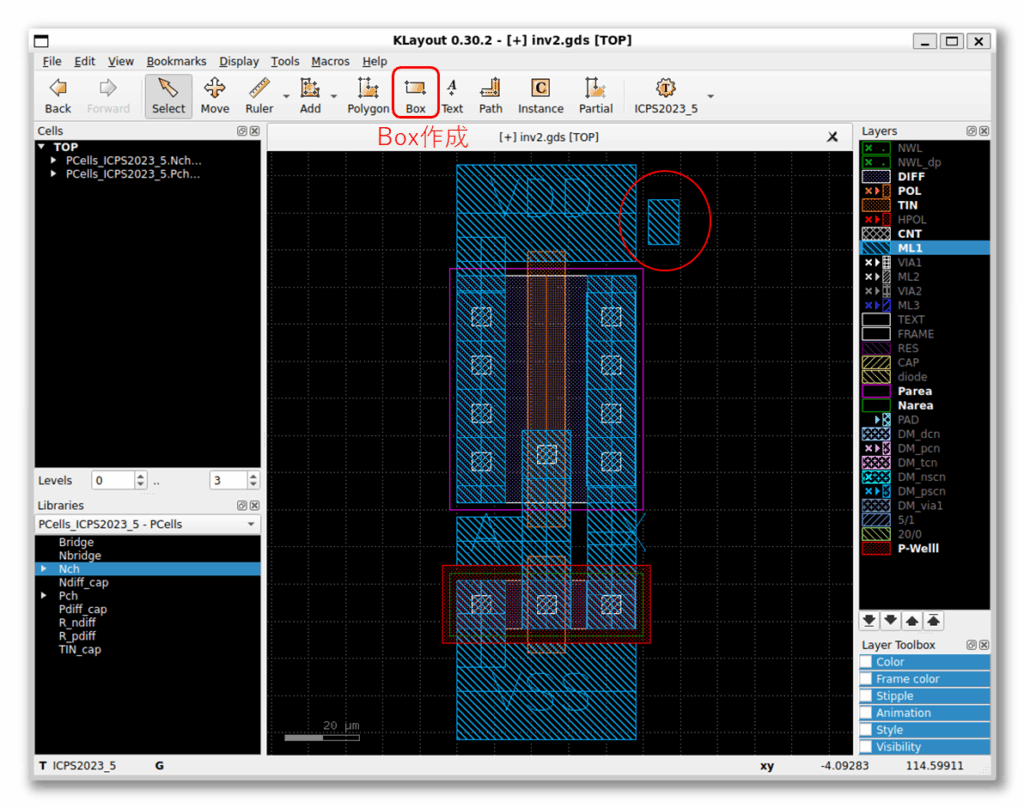

- 試しに、わざとエラーを作ってみます。

- KLayoutで、下記のようにメタル間隔が4umよりも短くなるように、ML1レイヤーのボックスを追加します。

- DRCを再実行して(Marker Databese Browserが起動したままなら、緑の三角ボタンをクリック)、エラーを確認します。

- Directory欄のチェック項目リストに黒文字の[Top]が表示されているので、三角マークをクリックして展開

- “(ML1-8)Ml1 space < 4” は、ML1レイヤーで間隔が4um以下になっていることを指摘しています。

- エラーの表示をクリックすると、Merker欄にフラグが、Info欄に座標が表示され、KLayoutの画面で、該当箇所が拡大表示されます。

[参考] 保存したGDSファイルを再読込した場合は、メニューに Tools – DRC – DRC for ICPS2023_5 が表示されないかもしれません。その場合は、メニューより、Macros – Macro Development を選び、Macro Development 画面で、DRCタブを選んでください。後述のLVSも同様です。

5.LVS (Layout vs Schematic)

LVSはパスしていなくても製造はできますがデバイス寸法や配線が間違っているので回路が動作しません。PDKにLVSの実行スクリプトが用意されているので、これを使ってみます。

LVSは、回路図から作成した参照ネットリストとレイアウト図から作成した抽出ネットリストを比較します。参照ネットリストを作成するため、Ngspiceのシミュレーション用ネットリストをworkディレクトリにコピーしてください。

cd ~/work

cp ~/.xschem/simulations/inv.spice ./- KLayoutのメニューより、Macros – Get referemce for ICPS2023_5 を選ぶと、入力ファイルを聞いてくるので、先程コピーした、inv.spiceを指定。~/work/lvs_workというディレクトリが作成され、参照ネットリストが保存されます。

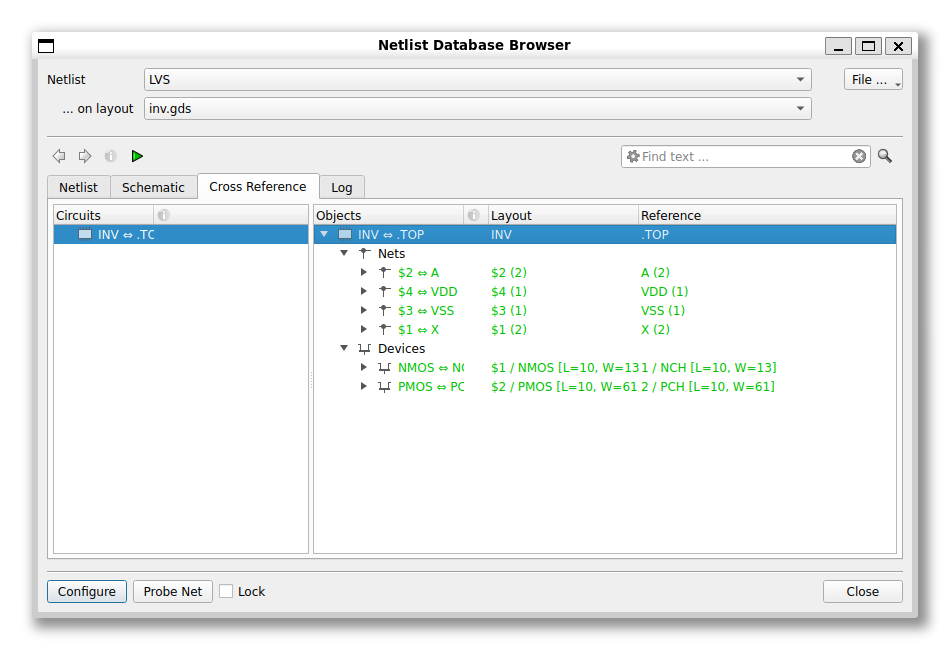

- メニューより、Tools – LVS – LVS for ICPS2023_5 を選ぶと、Netlist Database Browser が表示されます。

- INV <-> TOPをダブルクリックして展開すると、配線とデバイスの対応関係が示されます。

- 全てグリーンであればLVSをパスしています。エラーがあると赤い停止アイコンが表示されます。

[注意] 回路図上では、MOSFETのB端子をS端子に接続しましたが、実際のレイアウトでは、MOSFETのボディがフローティングとなっています。レイアウトからネットリストを抽出するとき、自動的にボディをソースに接続した形でネットリストが作成されるようです。

通常、完全空乏型のSOI MOSFETは、特にボディの電位をコントロールする必要がなければ、ボディをフローティング状態にして使用しますが、回路シミュレーションでは、(VDD, VSSではなく)ソースに接続することを推奨します。フローティング端子があると、回路シミュレーションが収束しにくくなります。

ただし、SOI MOSFETのボディをフローティングにした場合と、ソース接続にした場合で、どの程度回路特性上の違いがあるのか不明です。また、PDKでは、BSIM3v3というMOSFETモデルが用意されていますが、このモデルではSOI特有の現象を表現できません。DC特性を見た限りでは、ボディをフローティングにした場合とソースに接続した場合で、大きな違いはないようですが、回路シミュレーションの結果は目安と考えたほうが良さそうです。

6.GDSファイル出力

レイアウトデータをメーカに提出するためには、GDS IIフォーマットのファイル(GDSファイルまたはGDSストリームと呼ばれる)が必要です。通常、レイアウトエディタのレイヤー構成と製造メーカのレイヤー構成は異なっているため、翻訳が必要になります。下記の操作で、製造用GDSファイルの出力を行います。

- KLayoutのメニューより、Macros – ICPS2023_5(SOI mixed) to SOI conversion を選択します。

- 作業ディレクトリに inv_converted.gds という変換されたGDSファイルが作成されています。

コメント

“ミニマルファブPDKによるフルカスタム設計実習” への1件のフィードバック

[…] KLayout でレイアウトを入力(マニマルファブPDKによるフルカスタム設計実習を参照) […]