ミニマルファブ用のスタンダードセルライブラリは開発中のようですが、ここで紹介するオープンソースセミカスタム開発環境Qflowには、スタンダードセルライブラリが何種類か付属しているので、これを使って動作確認してみます。ただし、対応する製造ラインがないので実際には製造ができません。本ページは、ほぼQflowのチュートリアルと同じなので、オプション設定等の詳細はこちらを御覧ください。

開発環境のインストールは、こちらの投稿を参考にしてください。

1.VerilogHDLファイルの準備

作業ディレクトリを /home/ユーザ名/work として説明します。

work 配下に、source, synthesis, layout の各ディレクトリを作成し、sourceディレクトリの下に、下記リンク先のファイル jcnt8.vを保存してください。

ダウンロード先 > jcnt8.v (右クリックで保存)

cd ~

mkdir work

cd work

mkdir source synthesis layout[参考] WindowsからWSLにファイルをコピーする場合は、エクスプローラのフォルダーツリー(左ペイン)で、Linux – Ubuntu を選び、ライブラリ欄(右欄)で、\home\<ユーザ名>\ の配下のディレクトリにコピー。

2.論理合成~配置配線

(1) Qflowの起動

workディレクトリから、Qflowを起動します。

cd ~/work

qflow gui &(2) Preparation

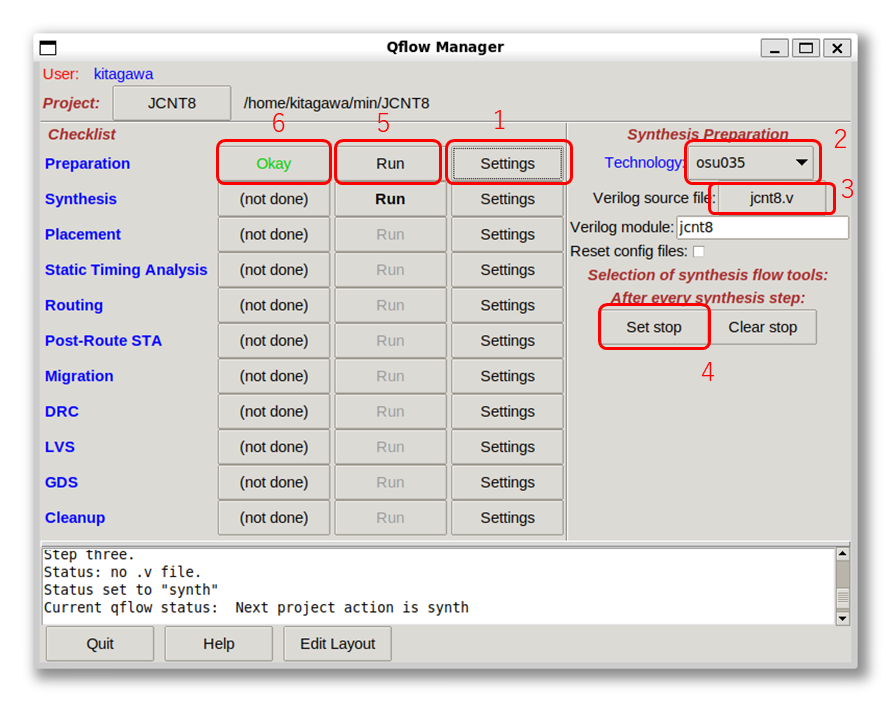

使用するテクノロジや入力ファイルなどの初期設定を行います。

- 初期設定がまだ済んでいないので、Preparation行のSettingsボタンをクリックして、上記の設定画面を表示させます。

- Technologyを選択します。ここでは、OSU035(Oklahoma State Univ CMOS 0.35um)を使ってみます。ライブラリ本体は、/usr/local/share/qflow/tech/osu035 にあります。

- Verilog source fileボタンをクリックして、設計対象となるVerilogHDLファイルを指定します。先程、保存しておいた work/source/jcnt8.v を選びます。トップモジュール名は自動的に表示されます。

- 初回はステップごとに停止させて、状況を確認する必要があるので、Set stopボタンをクリックします。全フローを流す場合は Clear stop ボタンを押します。

- 以上の設定が完了したら、Runボタンをクリックします。

- 問題がなければ、左側のボタンがOkay(緑)となります。エラーが有るとFail(赤)となります。左側のボタンをクリックすると実行ログが表示されます。

(3) Synthesis

論理合成を行います。特に設定はなく、SynthesisステップのRunボタンをクリックします。VerilogHDL記述に誤りがなければ、Okayとなるはずです。

(4) Placement

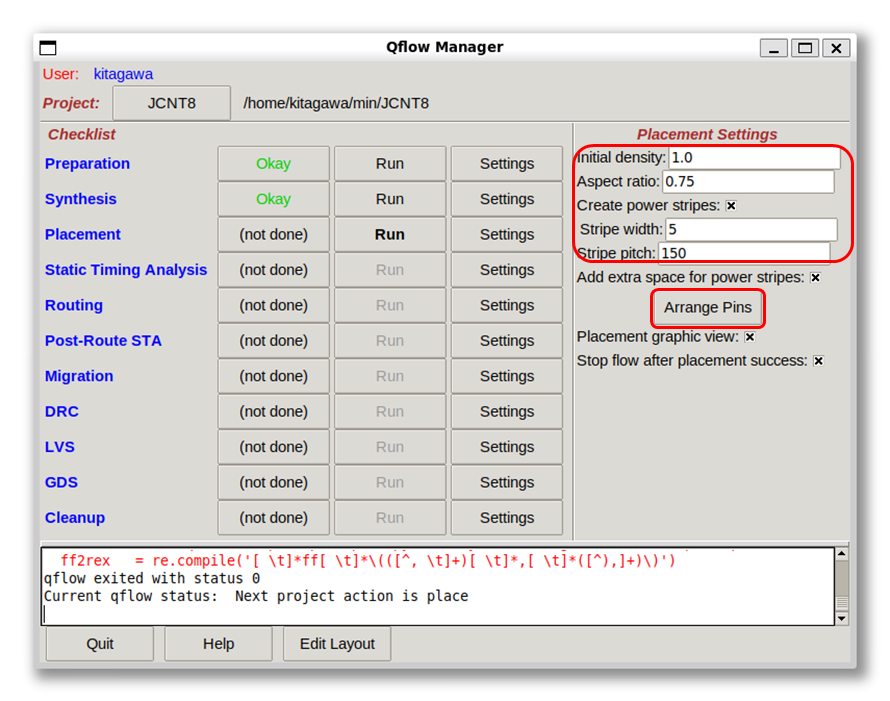

フロアプランおよびスタンダードセルの自動配置配線を行います。

- Placement Settings 欄の値を決めます。ここではデフォルトのままにします。配置配線がFailになる場合は、Initial densityを下げるか、Aspect ratioを変えてやり直してみます。Stripe widthは電源配線ストライプの幅、Stripe pitchは電源配線ストライプの間隔です。

- それでも配線がうまく出来ない場合は、<作業ディレクトリ>/layout/プロジェクト名.par というファイルをテキストエディタで開き、*rowSep : 0 0 の行を、*rowSep : 0.2 0 などに増やしてみます(0 ~ 1 ぐらい)。rowSep は、セルの行間隔です。

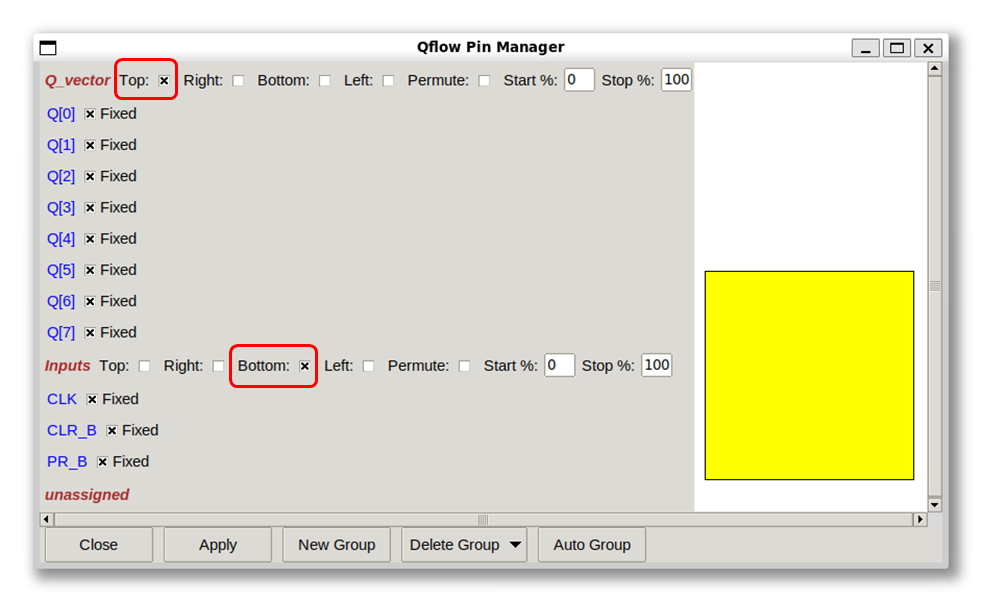

- Arrange Pinsボタンをクリックし、ピン配置の制約条件を設定します。設定しないと配線の都合でランダム配置になるようです。ここでは、下図のように 設定してください。(設定しても必ずしもそのとおりにはならないようです。)

- New Groupボタンで、Q_vectorグループとInputsグループを作る。

- QグループにQ[0]~Q[7]、Inputsグループに CLK, CLR_B, PR_B を入れます。マススでドラッグすると、ピン名を移動させることができます。

- 不要なグループは、Delete Groupボタンで削除できます。

- Q_vectorグループはTopにチェックを入れます。Inputsグループは

- Bottomにチェックを入れます。

- 全てのピン名についてFixed(順序の入れ替えを許可しない)にチェックを入れてください。反時計回りになるようピン配置が制約されます。

- Apply ボタンをクリックして設定を反映させます。

- [参考] Auto Groupeボタンで適当に設定して、Applyボタンをクリックすると、work/layoutディレクトリに、jcnt8.cel2というピン配置ファイルが作成されるので、これをテキストエディタで編集したほうが楽かもしれません。

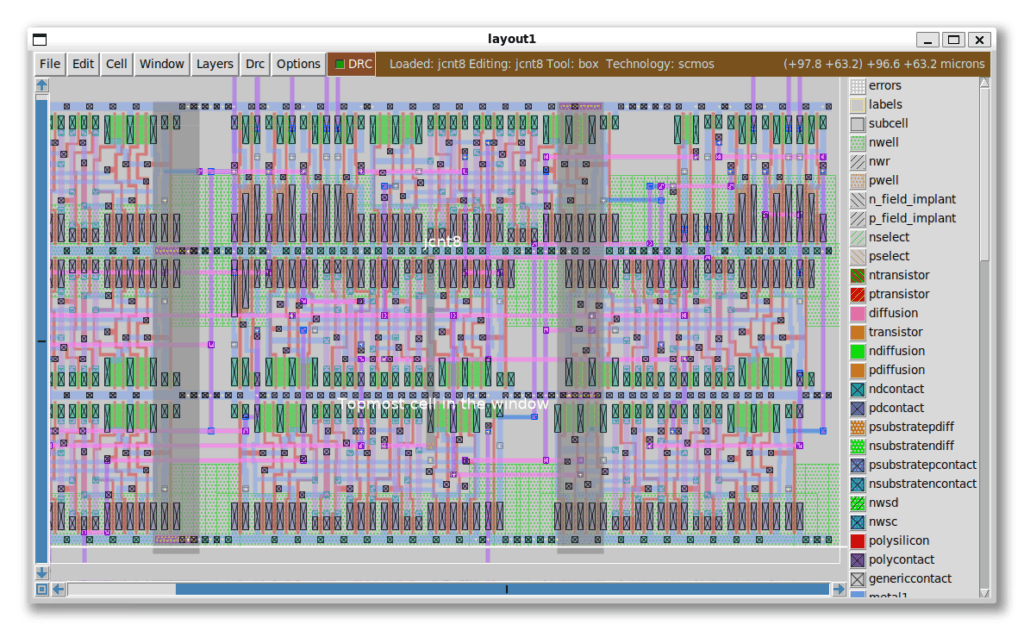

以上の設定が終わったら、PlacementステップのRunボタンをクリックしてください。配置配線が終わったら、QfowのGUI画面の下の方にあるEdit LayoutボタンでMagicを起動し、配置配線結果を確認します。

Qflowで生成した最終のgdsファイル(レイアウト図)は、なぜかピン名が表示されないようなので(配線名から辿れば分からないこともないけど間違える可能性が大きい)、ピンの位置をメモしておくと便利です。

(5) Static Timing Analysis

STAを行います。特に設定はなく、SynthesisステップのRunボタンをクリックします。右のOkayボタン(またはFailボタン)からタイミングレポートを見ることができます。この回路例では、エラーが出ないはずです。

いろいろな回路を試してみたところ、クロック系統が複数ある複雑な回路やマルチレートフィルタでは、どうしてもセットアップタイム違反、ホールドタイム違反によるエラーが回避できない場合があるようです。原因が不明ですが、クロックツリー合成が上手くできていないように見えます。STAでエラーとなっても、後で論理シミュレーションにより動作確認することにして、先に進む場合は、Static Timing AnalysisのSettingボタンをクリックして、Continue flow if STA failure にチェックを入れてSTAを実行します。

(6) Routing

詳細配線を行います。Route layers(使用する配線層数)の設定はデフォルト(全層使用 = max)のままで、SynthesisステップのRunボタンをクリックします。

(7) Post-Route STA

詳細配線結果のSTAを行います。デフォルト設定のままRunボタンをクリックし、右のOkayボタン(またはFailボタン)からタイミングレポートを確認します。

(8) Migration

レイアウトを標準的なDEFフォーマットからMagicデータベースに変換します。DRC, LVSで必要なようです。

(9) DRC (Design Rule Check)

設計規則チェックを行います。Use GDS view of standard cells にチェックを入れて、実行してください。

(10) LVS (Layout vs Schematic)

回路図(ネットリスト)とレイアウトの等価性検証を行います。設定はないので、そのまま実行です。

(11) GDS

設計を再利用する場合や製造を行うときに必要となるGDS II フォーマットのレイアウトデータを出力します。Use GDS view of standard cells にチェックを入れて実行してください。GUI画面の下の方にあるEdit LayoutボタンでMagicを起動し、最終結果を確認します。

(12) Cleanup

途中からやり直す場合に必要なファイルを残して、不要な中間ファイルを消去するようです。Purgeにチェックをいれて実行すると、最初からやり直しとなります。ただし、Purgeをチェックしなくても、詳細配線後のネットリストは消されるようです。

3.動作確認

Qflowを実行すると、work/synthesisディレクトリの下に、下記のVerilogHDLネットリストが作成されているので、これらを使って遅延を考慮した論理シミュレーションを行います。

| ステップ | ファイル名 | 備考 |

|---|---|---|

| 論理合成後 | jcnt8.rtlnopower.v | |

| 配置配線後 | jcnt8_synth.rtlnopower.v | |

| 詳細配線後 | jcnt8_postroute.v | Cleanupにより削除される |

(1) VerilogHDLファイルの準備

ここでは、シミュレータとして、Icarus Verilogを使用しますが、Icarus Verilogは、入出力ポートの宣言を、ポートリストと分けて書かないと怒るので、jcnt8.rtlnopower.v をテキストエディタで開いて、下記の例のように修正を行います。

// 修正前

module jcnt8(

input CLK,

input CLR_B,

input PR_B,

output [7:0] Q

);// 修正後

module jcnt8(CLK, CLR_B, PR_B, Q);

input CLK;

input CLR_B;

input PR_B;

output [7:0] Q; テストベンチ記述を下記リンクからダウンロードして、work/synthesisの下にコピーしてください。

ダウンロード先 > tb_jcnt8_syn.v (右クリックで保存)

[注意] Qflowで生成されたVerilogネットリストは、ポートの順序が勝手に変更されているようです。テストベンチを作成する際に、テスト対象回路と信号の接続は、ポート順序ではなく、下記の例のように、名前による接続で記述するようにしてください。

jcnt8 DUT(.CLK(r_clk), .CLR_B(r_clr_b), .PR_B(r_pr_b), .Q(w_q));スタンダードセル(論理ゲート)のVerilogHDL記述を使用するため、下記のコマンドによりシンボリックリンクを作成してください。

cd ~/work/synthesis

ln -s /usr/local/share/qflow/tech/osu035/osu035_stdcells.v osu035_stdcells.v (2) シミュレーションの実行

下記のコマンドで、実行形式のシミュレーションファイルを作成します。スタンダードセルに対して警告が出ますが無視してください。

cd ~/work/synthesis

iverilog tb_jcnt8_syn.v jcnt8.rtlnopwr.v osu035_stdcells.vエラーがなければ、a.outという実行ファイルが作成されますので、これを実行すします。

./a,outtb_jcnt8_syn.vcd というVCD(Value Change Dump)ファイルが作成されます。

(3) 波形表示

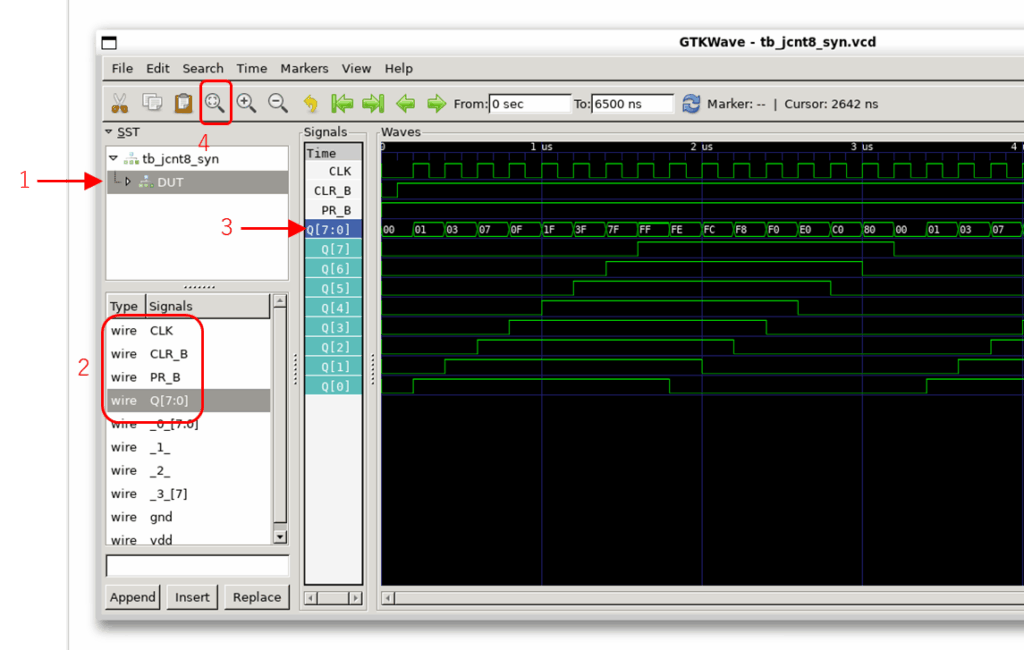

GTKwaveを使ってタイミングシミュレーションの結果を表示してみます。

gtkwave tb_jcnt8_syn.vcd &

- 検証したいモジュールをクリックします。ここでは、DUTです。

- 確認したい信号名をクリックします。ここでは、CLK, CLR_B, PR_B, Q[7:0] です。

- Q[7:0]をダブルクリックして、ビット毎に表示します。

- 虫眼鏡アイコンをクリックして波形全体を表示します。

この回路は、ジョンソンカウンターです。出力Qを展開した波形を見ると、正常動作していることが分かります。